H- 브리지 회로에서 P- 채널 MOSFET을 구현하는 것은 쉽고 매력적으로 보일 수 있지만 최적의 응답을 얻기 위해 몇 가지 엄격한 계산과 매개 변수가 필요할 수 있습니다.

P 채널 MOSFET은 일반적으로 부하 ON / OFF 스위칭을 위해 구현됩니다. 높은 쪽의 P- 채널 옵션의 사용이 용이하여 저전압 드라이브 (H- 브리지 네트워크) 및 비 절연 부하 점 (벅 컨버터)과 같은 애플리케이션과 다음과 같은 애플리케이션에 매우 편리하게 사용할 수 있습니다. 공간은 중요한 제한 사항입니다.

P 채널 MOSFET의 주요 이점은 하이 사이드 스위치 위치에 대한 경제적 인 게이트 구동 전략이며 일반적으로 시스템을 매우 비용 효율적으로 만드는 데 도움이됩니다.

이 기사에서는 H 브리지 애플리케이션을위한 하이 사이드 스위치로 P 채널 MOSFET을 사용하는 방법을 살펴 봅니다.

P- 채널 대 N- 채널 장단점

언제 하이 사이드 스위치 애플리케이션에 사용 N 채널 MOSFET의 소스 전압은 접지와 관련하여 증가 된 전위에 있습니다.

따라서 여기서 N 채널 MOSFET을 작동하려면 부트 스트래핑 회로와 같은 독립적 인 게이트 드라이버 또는 펄스 트랜스포머 스테이지를 포함하는 배열이 필요합니다.

이러한 드라이버에는 별도의 전원이 필요하지만 변압기 부하는 때때로 호환되지 않는 상황을 겪을 수 있습니다.

반면에 이것은 P 채널 MOSFET의 상황이 아닐 수 있습니다. 일반 레벨 시프터 회로 (전압 레벨 체인저)를 사용하여 P 채널 하이 사이드 스위치를 쉽게 구동 할 수 있습니다. 이를 달성하면 회로가 간소화되고 모든 비용이 효과적으로 절감됩니다.

하지만 여기서 고려해야 할 점은 동일한 R을 얻는 것이 매우 어려울 수 있다는 것입니다.DS (켜짐)유사한 칩 치수를 사용하는 N- 채널과는 대조적으로 P- 채널 MOSFET의 효율성.

N 채널에서 캐리어의 흐름이 P 채널보다 약 2 ~ 3 배 더 큽니다.DS (켜짐)범위 P- 채널 장치는 N- 채널 장치보다 크기가 2 ~ 3 배 더 커야합니다.

패키지 크기가 클수록 P 채널 장치의 열 내성이 감소하고 현재 사양도 증가합니다. 이것은 또한 증가 된 케이스 크기로 인해 동적 효과에 비례하여 영향을 미칩니다.

따라서 전도 손실이 높은 경향이있는 저주파 애플리케이션에서 P 채널 MOSFET은 R을 가져야합니다.DS (켜짐)N 채널에 해당합니다. 이러한 상황에서 P 채널 MOSFET 내부 영역은 N 채널보다 커야합니다.

또한 일반적으로 스위칭 손실이 높은 고주파 애플리케이션에서 P 채널 MOSFET은 N 채널에 필적하는 게이트 전하 값을 가져야합니다.

이와 같은 경우 P 채널 MOSFET 크기는 N 채널과 동등 할 수 있지만 N 채널 대안에 비해 전류 사양이 감소합니다.

따라서 이상적인 P 채널 MOSFET은 적절한 R을 고려하여 신중하게 선택해야합니다.DS (켜짐)및 게이트 충전 사양.

애플리케이션 용 P 채널 MOSFET을 선택하는 방법

P 채널 MOSFET을 효과적으로 적용 할 수있는 다양한 스위칭 애플리케이션이 있습니다 (예 : 저전압 드라이브 및 비 절연 부하 점).

이러한 유형의 애플리케이션에서 MOSFET 선택을 관리하는 중요한 지침은 일반적으로 장치 ON 저항 (RDS (켜짐)) 및 게이트 차지 (Q지). 이러한 변수 중 하나는 애플리케이션의 스위칭 주파수에 따라 더 중요합니다.

풀 브리지 또는 B6 브리지 (3 상 브리지) 구성과 같은 저전압 드라이브 네트워크에 적용하기 위해 N 채널 MOSFET이 일반적으로 사용됩니다. 모터 (부하) 및 DC 공급 장치 포함.

N- 채널 장치가 제공하는 긍정적 인 측면에 대한 타협 요인은 게이트 드라이버 설계의 복잡성입니다.

N 채널 하이 사이드 스위치의 게이트 드라이버는 부트 스트랩 회로 모터 전압 공급 레일보다 더 큰 게이트 전압을 생성하거나 또는 독립적 인 전원 공급 장치를 사용하여 전원을 켭니다. 설계 복잡성이 증가하면 일반적으로 설계 작업과 조립 영역이 증가합니다.

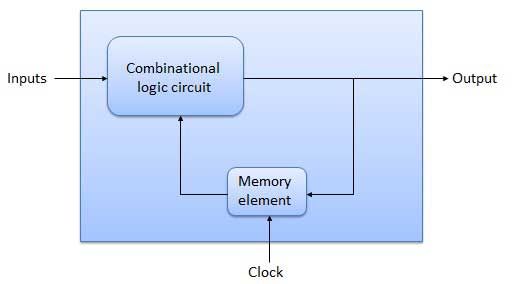

아래 그림은 상보 형 P 및 N 채널 MOSFET을 사용하여 설계된 회로와 4 개의 N 채널 MOSFET 만 사용하는 회로 간의 차이점을 보여줍니다.

4 개의 N 채널 MOSFET 만 사용

이 배열에서 하이 사이드 스위치가 P 채널 MOSFET으로 구축 된 경우 드라이버 설계는 아래와 같이 레이아웃을 엄청나게 단순화합니다.

P 및 N 채널 MOSFET 사용

부트 스트랩의 필요성 충전 펌프 하이 사이드 스위치를 전환하기 위해 제거됩니다. 여기에서는 입력 신호와 레벨 시프터 (3V ~ 5V 컨버터 또는 5V ~ 12V 컨버터 스테이지)를 통해 간단히 구동 할 수 있습니다.

스위칭 애플리케이션을위한 P 채널 MOSFET 선택

일반적으로 저전압 드라이브 시스템은 10 ~ 50kHz 범위의 스위칭 주파수로 작동합니다.

이 범위에서 거의 모든 MOSFET 전력 손실은 모터의 고전류 사양으로 인해 전도 손실을 통해 발생합니다.

따라서 이러한 네트워크에서 적절한 R을 가진 P 채널 MOSFETDS (켜짐)최적의 효율성을 달성하기 위해 선택해야합니다.

이것은 12V 배터리로 작동하는 30W 저전압 드라이브의 예시를 고려하면 이해할 수 있습니다.

하이 사이드 P 채널 MOSFET의 경우 두 가지 옵션이있을 수 있습니다. 하나는 동등한 R을 갖습니다.DS (켜짐)낮은 쪽 N- 채널과 비슷하고 게이트 전하가 비슷한 다른 채널과 비슷합니다.

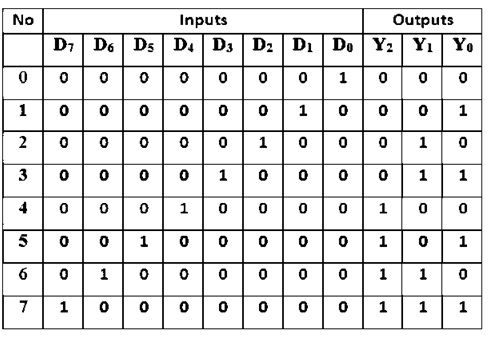

아래 표는 비슷한 R을 갖는 풀 브리지 저전압 드라이브에 적용 할 수있는 구성 요소를 보여줍니다.DS (켜짐)그리고 낮은 쪽의 N- 채널 MOSFET과 동일한 게이트 전하를 사용합니다.

특정 애플리케이션 내의 MOSFET 손실을 설명하는 위의 표는 다음 파이 차트에서 입증 된 바와 같이 전체 전력 손실이 전도 손실에 의해 지배된다는 것을 보여줍니다.

또한 N 채널과 비슷한 게이트 전하를 갖는 P 채널 MOSFET이 선호된다면 스위칭 손실은 동일하지만 전도 손실은 아마도 지나치게 높을 수 있습니다.

따라서 낮은 주파수를 사용하는 낮은 스위칭 애플리케이션의 경우 하이 사이드 P 채널 MOSFET은 미친 듯이 비슷한 R을 가져야합니다. DS (켜짐) 로우 사이드 N- 채널처럼.

비 절연 부하 점 (POL)

비 절연 부하 점은 출력이 입력과 분리되지 않는 벅 컨버터와 같은 컨버터 토폴로지입니다. 플라이 백 디자인 입력 및 출력 단계가 완전히 분리되어 있습니다.

출력 전력이 10W 미만인 저전력 비 절연 부하 점의 경우 가장 큰 설계 어려움 중 하나를 제시합니다. 만족스러운 수준의 효율성을 유지하면서 크기를 최소화해야합니다.

컨버터 크기를 줄이는 한 가지 인기있는 방법은 N 채널 MOSFET을 하이 사이드 드라이버로 사용하고 작동 주파수를 상당히 높은 수준으로 높이는 것입니다. 더 빠른 스위칭을 통해 훨씬 축소 된 인덕터 크기를 사용할 수 있습니다.

쇼트 키 다이오드는 종종 이러한 유형의 회로에서 동기식 정류를 위해 구현되지만 MOSFET의 전압 강하는 일반적으로 다이오드보다 훨씬 낮기 때문에 MOSFET이 더 나은 옵션입니다.

또 다른 공간 절약 접근법은 하이 사이드 N 채널 MOSFET을 P 채널로 대체하는 것입니다.

P- 채널 방식은 게이트를 구동하기위한 복잡한 보조 회로를 제거하며, 이는 하이 사이드의 N- 채널 MOSFET에 필요합니다.

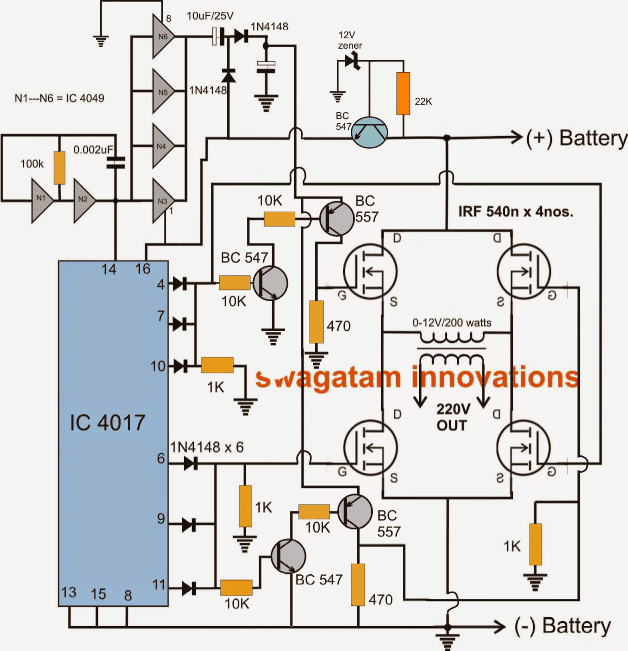

아래 다이어그램은 하이 사이드에 구현 된 P 채널 MOSFET이있는 벅 컨버터의 기본 설계를 보여줍니다.

일반적으로 비 절연 부하 점 (Point of Load) 애플리케이션의 스위칭 주파수는 500kHz에 가깝거나 최대 2MHz까지 높을 수 있습니다.

초기 설계 개념과는 달리 이러한 주파수에서 주요 손실은 스위칭 손실로 밝혀졌습니다.

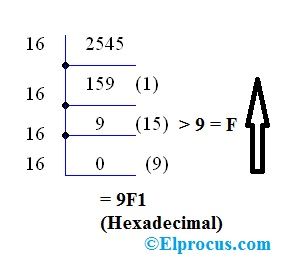

아래 그림은 1MHz의 스위칭 주파수에서 실행되는 3 와트 비 절연 부하 점 애플리케이션에서 MOSFET의 손실을 나타냅니다.

따라서 하이 사이드 N- 채널 디바이스와 관련하여 하이 사이드 애플리케이션으로 선택 될 때 P- 채널에 지정되어야하는 게이트 전하 레벨을 보여줍니다.

결론

P 채널 MOSFET을 적용하면 설계자가 덜 복잡하고 신뢰성이 높으며 구성이 향상된다는 이점이 있습니다.

즉, 주어진 응용 프로그램에 대해 R 간의 타협은DS (켜짐)그리고 Q지P 채널 MOSFET을 선택하는 동안 신중하게 평가해야합니다. 이는 p- 채널이 n- 채널 변형처럼 최적의 성능을 제공 할 수 있도록하기위한 것입니다.

예의: 인피니언

이전 : 모기 찰싹 때리기 박쥐를 복구하는 방법 다음 :자가 동력 발전기 만들기

![IC 4060 래칭 문제 [해결됨]](https://electronics.jf-parede.pt/img/timer-delay-relay/35/ic-4060-latching-problem.jpg)