의 주요 단점 조합 회로 즉, 현재 및 이전 상태를 저장하는 데 메모리를 사용하지 않습니다. 따라서 이전 입력 상태는 회로의 현재 상태에 영향을 미치지 않습니다. 반면 순차 회로에는 메모리가 있으므로 출력은 입력에 따라 달라질 수 있습니다. 이 유형의 회로는 이전 입력, 출력, 클록 및 메모리 요소를 사용합니다. 여기서 메모리 요소는 래치 또는 플립 플롭 일 수 있습니다. 순차 회로는 ROM, 플립, PLA, CPLD (복잡한 프로그래밍 가능 논리 장치) , FPGA (필드 프로그래밍 가능 게이트 어레이) . 이 기사에서는 PLA를 사용하여 순차 회로를 설계하는 방법에 대해서만 설명합니다.

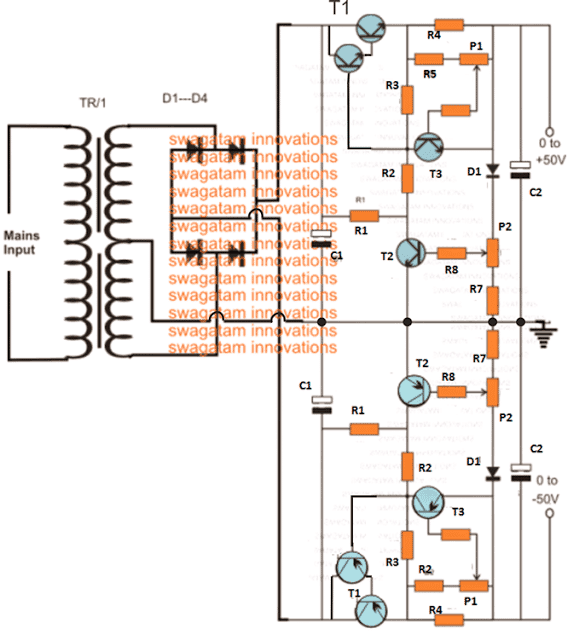

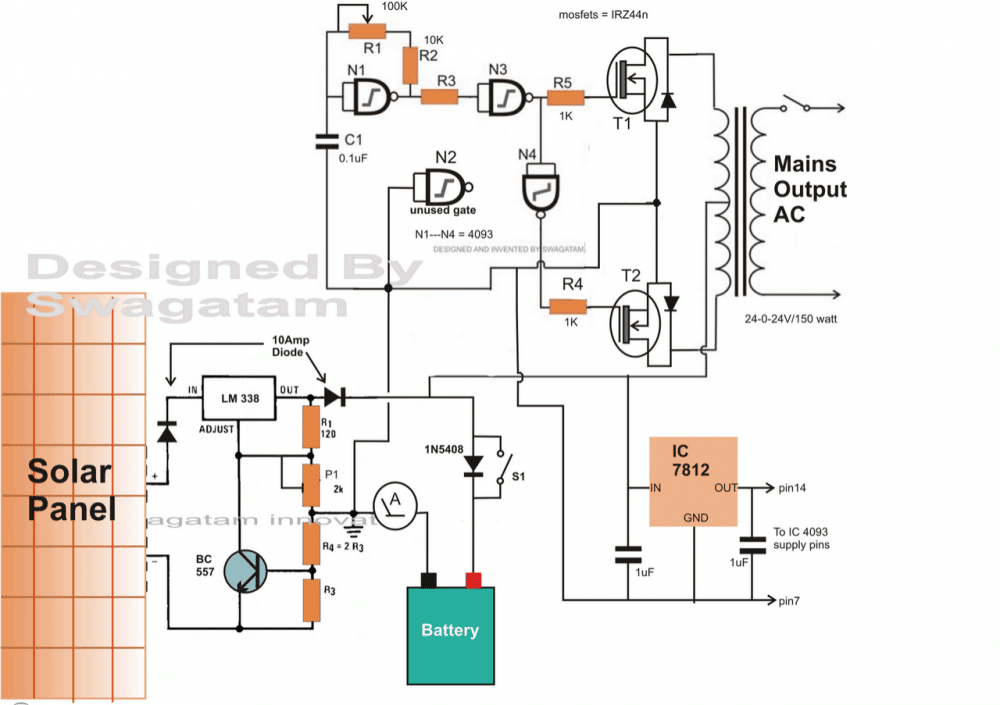

다음과 같은 순차 회로의 블록 다이어그램 :

순차 회로의 블록 다이어그램

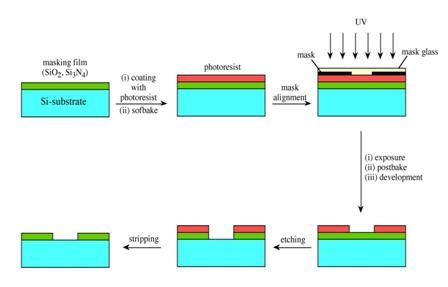

PLA를 이용한 순차 회로 설계

순차 회로 PLA (Programmable Logic Arrays) 및 플립 플롭을 사용하여 구현할 수 있습니다. 이 설계에서는 상태 할당이 중요 할 수 있습니다. 좋은 상태 할당을 사용하면 필요한 제품 용어 수를 줄여 필요한 PLA 크기를 줄일 수 있기 때문입니다. 리터럴의 결합으로 정의 된 제품 용어로, 각 리터럴은 변수 또는 부정입니다.

디자인을 코드 변환기로 고려해 보겠습니다. 아래 표에 표시된 상태 테이블은 PLA 1 개와 PLA 3 개를 사용하여 구현할 수 있습니다. 플립 플롭 아래 그림과 같이. 이 회로 구성은 ROM이 적절한 크기의 PLA로 대체된다는 점을 제외하면 ROM 플립 플롭 기반 설계와 매우 유사합니다. 상태 할당은 아래 주어진 진리표로 이어집니다. 이 테이블은 4 개의 입력, 13 개의 제품 용어 및 4 개의 출력이있는 PLA에 저장할 수 있지만 16 워드 ROM에 비해 크기가 거의 줄어들지 않습니다.

| X 1 분기 2 분기 3 분기 | D1 D2 D3 사용 |

| 0 0 0 0 0 0 0 1 0 0 1 0 010 1 1 0 1 0 0 010 1 010 012 1 1 1 0 0 0 1 0 0 1 1010 10 1 1 1 1 0 0 1 1 0 1 1 1 0 1 1 1 1 | 1 0 0 1 10 1 1 0 1 0 0 010 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 010 1 0 0 0 X X X X X X X X |

표 : 진실 표

선물 상태

| 다음 주 X = 01 | 선물 출력 (Z) |

| 에 | B C | 1 0 |

비 씨 | D E 그리고 E | 1 0 0 1 |

디 IS | H H H M | 0 1 1 0 |

H 미디엄 | A A 받는 사람- | 0 1 1 - |

표 : 상태 표

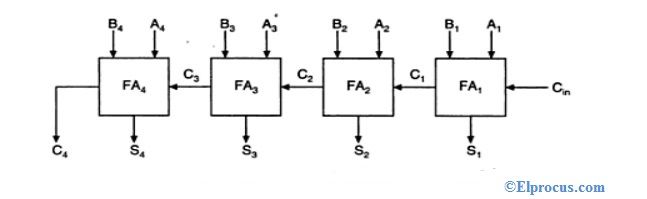

PLA를 사용한 순차 회로 설계

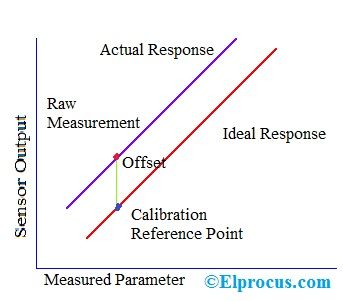

Karnaugh 맵에서 파생 된 입력 출력 방정식

여기에는 7 개의 상태가 있으므로 3 개의 D 플립 플롭이 필요합니다. 따라서 4 개의 입력과 4 개의 출력을 가진 PLA 회로가 필요합니다. 코드 변환기의 상태 할당을 고려하면 Karnaugh에서 파생 된 결과 출력 방정식과 D 플립 플롭 입력 방정식을 다음 방정식으로 작성할 수 있습니다.

D1 = Q1 + = Q2”

D2 = Q2 + = Q2”

D3 = Q3 + = Q1 Q2 Q3 = X”Q1 Q3”= X Q1”Q2”

Z = X 'Q3'+ X Q3

| X 1 분기 2 분기 3 분기 | D1 D2 D3 사용 |

--0- - 1 - - -11 1 0 1-0 1 0 0- 0--0 열한

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

이 방정식에 해당하는 PLA 표는 위의 표에 나와 있습니다. 이 테이블은 4 개의 입력, 7 개의 제품 용어 및 4 개의 출력이있는 PLA를 사용하여 실현할 수 있습니다. 처음에 위 설계의 작동을 확인하려면 X = 0 및 Q1Q2Q3 = 000이라고 가정합니다. 이렇게하면 테이블에서 – – 0- 및 0 – – -0 행이 선택되므로 Z = 0 및 D1D2D3 = 100입니다. 활성 클럭 에지 이후 Q1Q2Q3 = 100. 다음 입력이 X = 1이면 – – 0 – 및 – 1- – 행이 선택되므로 Z = 0 및 D1D2D3 = 110입니다. 활성 클록 에지 이후, Q1Q2Q3 = 110.

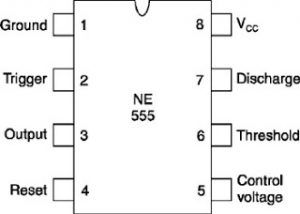

프로그래밍 가능 논리 어레이 (PLA)

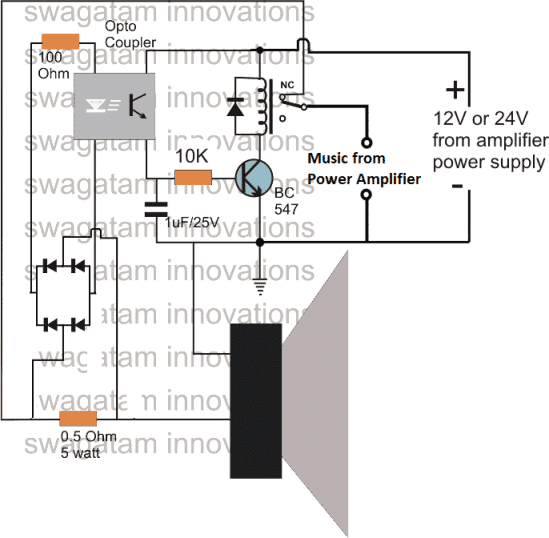

프로그래밍 가능 논리 어레이는 프로그래밍 가능 논리 장치입니다. 일반적으로 조합 논리 회로를 구현하는 데 사용됩니다. PLA에는 프로그래밍 가능한 AND 평면 (AND 어레이) 세트가 있으며, 이는 일련의 프로그래밍 가능한 OR 평면 (OR 어레이)에 연결되어 출력을 생성하기 위해 잠정적으로 보완 될 수 있습니다. 이 레이아웃을 사용하면 많은 논리 기능을 제품 합계 (SOP) 표준 형식. PLA의 간단한 블록 다이어그램은 다음과 같습니다.

PLA의 블록 다이어그램

PLA와 PAL (프로그래밍 가능한 어레이 로직)의 주요 차이점은 다음과 같습니다.

PLA : 둘 다 AND 평면 및 OR 평면 프로그래밍 가능합니다.

PAL : AND 평면 만 프로그래밍 할 수 있지만 OR 평면은 고정되어 있습니다.

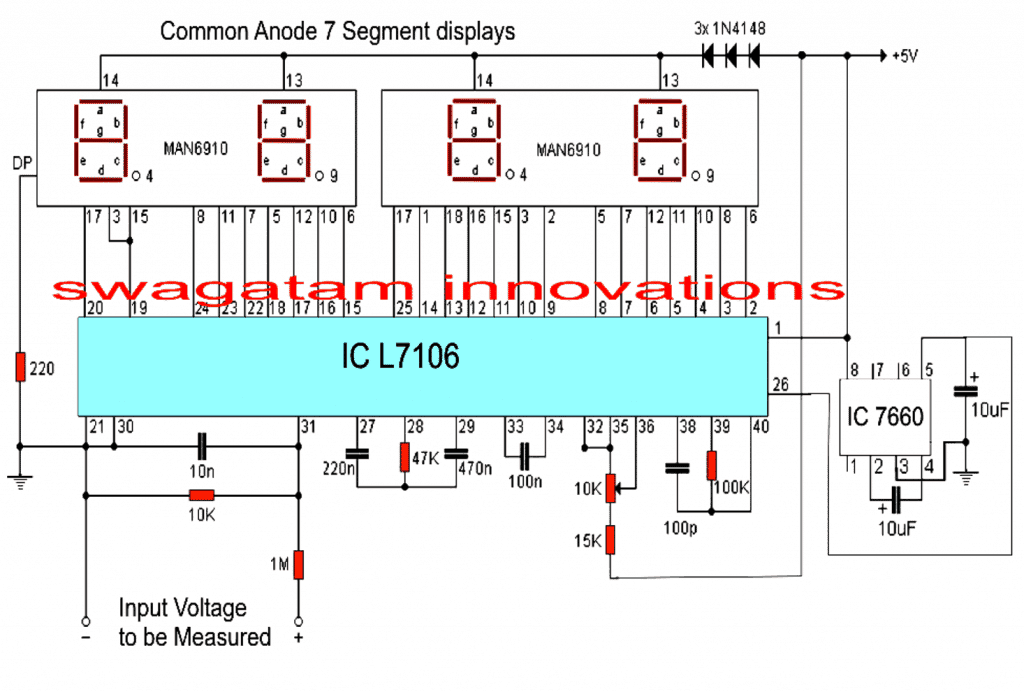

PLA에 대한 더 나은 이해를 위해 아래 예를 고려합니다.

이 함수를 구현해 봅시다 f1과 f2는 다음과 같이 주어집니다.

입력 x1, x2, x3 및 각각의 보완 된 신호는 프로그래밍 가능한 AND 평면에 제공되며, 여기서 우리는 minterms라고하는 P1, P2, P3으로 AND 평면 출력을 얻습니다. 그런 다음 이러한 신호는 프로그래밍 가능한 OR 평면에 제공되어 필요한 출력 함수 f1 및 f2 (제품 합계)를 생성합니다. 아래 그림은 특정 기능에 대한 PLA의 게이트 레벨 구현을 설명합니다.

PLA의 구현

이것은 PLA를 사용한 순차 회로 설계에 관한 것입니다. 이 기사에 제공된 정보는이 개념을 더 잘 이해하는 데 도움이된다고 생각합니다. 또한이 기사에 관한 질문이나 전기 및 전자 프로젝트 구현 , 아래 댓글 섹션에 댓글을 달아 저희에게 접근 할 수 있습니다. 여기에 질문이 있습니다. 순차 회로 란 무엇입니까?