Brent-Kung 가산기는 1982년 Hsiang Te Kung과 Richard Peirce Brent에 의해 제안되었습니다. 유연성으로 인해 디지털 디자인에서 널리 사용되는 Parallel Prefix adder 또는 tree adder입니다. 병렬 접두사 추가기는 논리 레벨 수에 따라 여러 가지 방법으로 구축될 수 있습니다. 논리 게이트 관련, 모든 게이트의 팬아웃 및 레벨 사이의 배선. 사용 가능한 트리 애더에는 다양한 유형이 있으며 기본 트리 애더는 Sklanskym KoggeStone 및 Brent-Kung입니다. KSA(Kogge-Stone 애더)와 비교하여 이 애더는 가산기 구조에 높은 규칙성을 제공하고 배선 차단이 적습니다. 이는 더 나은 성능과 더 적은 칩 영역으로 이어집니다. 이 문서에서는 다음 사항에 대한 간략한 정보를 제공합니다. 브렌트 쿵 애더 .

브렌트 쿵 애더(Brent Kung Adder)란 무엇입니까?

결과를 얻기 위해 최소 회로를 사용하는 가산기는 브렌트 쿵 가산기(Brent Kung Adder)로 알려져 있으며 저전력 가산기 또는 병렬 가산기라고도 합니다. 이 가산기는 칩 크기를 줄여 이러한 가산기를 제조하기가 더 쉬워지도록 고안되었습니다. 이 가산기의 대칭 및 일반적인 구성 구조는 생산 비용을 크게 절감하고 파이프라인 토폴로지에 사용할 수 있습니다. 상보형 패스 트랜지스터 로직을 활용하면 다음과 같은 설계 성능을 향상하는 데 도움이 됩니다. 멀티플렉서 다양한 셀 디자인에 접근합니다.

브렌트 쿵 가산기 회로

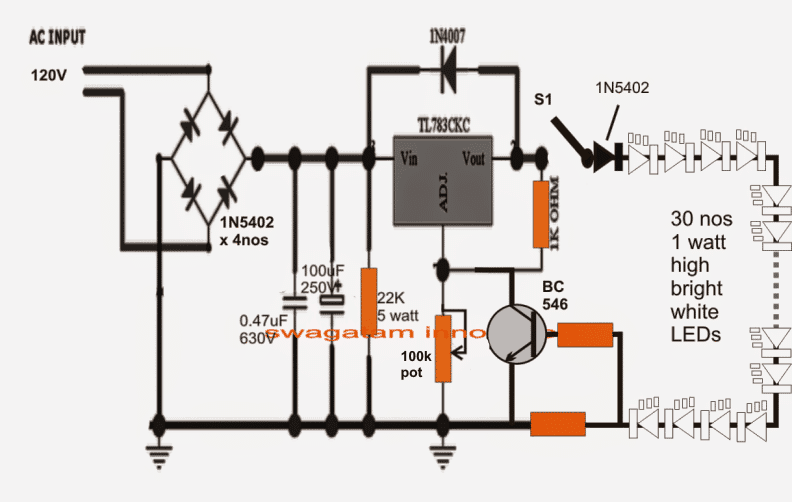

아래에는 1단계(전처리 단계), 2~7단계가 캐리 생성 단계, 8단계가 후처리를 포함하는 브렌트쿵 병렬 접두사 가산기 다이어그램이 나와 있습니다. 이는 고급 아키텍처이며 구성이 매우 간단하고 배선 혼잡이 적습니다. 따라서 배선이 적으면 아키텍처를 실행하는 데 필요한 공간이 줄어듭니다. 또한 더 적은 수의 전선이 교차(또는) 겹치기 때문에 라우팅이 훨씬 쉬워집니다. 그러나 단수 증가로 인해 지연 시 페널티가 증가하고, 이 가산기에 대한 팬아웃이 증가하여 지연 시간도 증가하게 됩니다.

브렌트 쿵 애더는 어떻게 작동하나요?

Brent Kung Adder는 4비트 그룹 접두사를 찾는 데 유용한 두 비트 그룹의 접두사를 계산하여 작동합니다. 이러한 접두사는 8비트 그룹의 접두사 등을 계산하는 데 사용됩니다. 그 후 이러한 접두사는 특정 비트 스테이지의 캐리아웃을 계산하는 데 사용됩니다. 이러한 캐리는 다음 단계의 그룹 전파와 함께 사용되어 해당 단계의 합계 비트를 계산합니다. Brent Kung Tree는 2log2N – 1단계를 사용합니다.

32비트 브렌트 쿵 애더

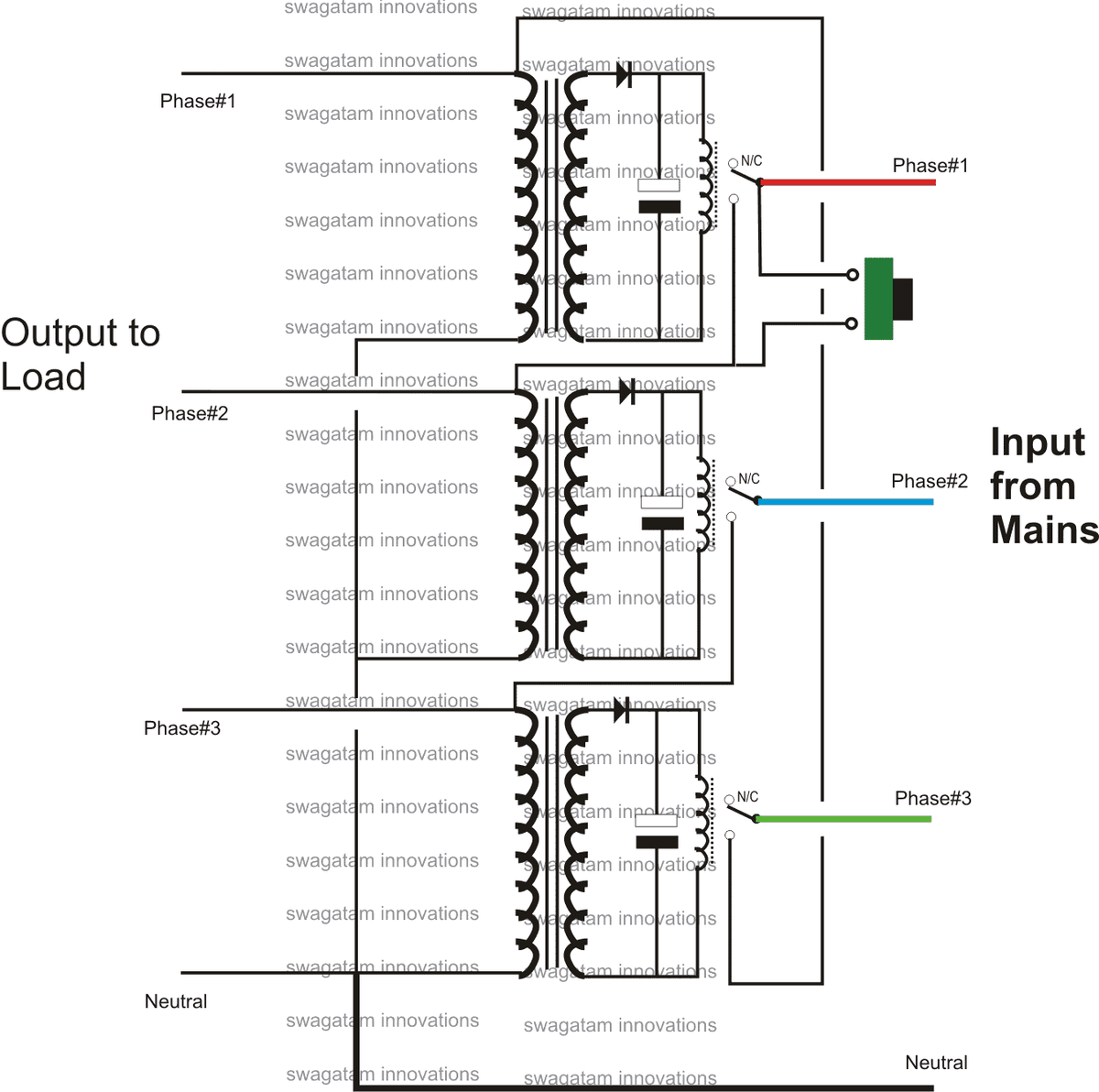

32비트 Brent Kung 가산기 레이아웃은 아래와 같습니다. 이 레이아웃의 시작 부분에서는 NAND, 인버터, XOR, NOR 등과 같은 기본 로직 게이트를 설계합니다. 이후 블랙 셀, 그레이 셀, 버퍼 및 PG 로직과 같은 필요한 셀을 로직 게이트로 설계합니다.

아래의 32비트 Brent Kung 가산기에서는 AOI 및 OAI와 같은 반전 게이트가 주로 회색 및 검정색 셀에 교대로 사용됩니다. 따라서 검정색 및 회색 셀은 회색 및 검정색 블록으로 표시되는 반면 버퍼는 원으로 표시됩니다.

A 및 B와 같은 입력은 블록 다이어그램에 표시된 PG 로직에 제공됩니다. 32비트 가산기의 경우 32개의 PG 논리 블록이 필요하며 전파(P) 및 생성(G) 신호는 이 블록의 출력입니다. 이러한 신호는 Brent Kung 가산기 트리 구조에 제공됩니다. 이 가산기의 구조는 회색 셀과 검정색 셀을 포함합니다.

회색 셀에는 3개의 입력과 단일 출력이 포함됩니다. 현재 단계의 전파 및 생성 신호와 이전 단계의 신호 생성은 입력이고 그룹 생성 신호는 o/p입니다. 모든 트리 구조에서 모든 단계는 회색 셀로 끝나고 이 셀의 o/p는 그룹 생성 신호입니다. 이 신호는 단순히 해당 단계의 캐리로 간주됩니다. 검정색 셀에는 4개의 입력과 2개의 출력이 포함됩니다. 이 셀의 입력은 현재 단계의 P & G 신호와 이전 단계의 P, G 신호입니다.

PG 로직에는 AND 및 XOR 게이트가 포함되어 있으며 AND 로직 게이트는 G 신호를 생성하는 데 사용되고 XOR 로직 게이트는 P 신호를 제공합니다. 불필요한 인버터를 없애기 위해 그레이 셀과 블랙 셀 두 종류를 활용합니다. 회색 셀의 한 행에 사용되는 반전 게이트는 AOI 또는 AND-OR-Inverter이고 다음 행 내의 검정색 셀의 반전 게이트는 OAI 또는 OR-AND-Inverter를 사용합니다. AOI 셀은 일반 입력을 사용하여 반전된 출력을 제공하는 반면 OAI는 반전된 입력을 사용하여 일반 출력을 제공합니다.

브렌트 쿵 애더 작업

Brent Kung 가산기는 고성능 덧셈 연산에 사용되는 병렬 접두어 가산기입니다. 이 가산기는 산술 연산을 수행하는 트리 구조처럼 보입니다. 이 가산기에는 검은색 셀과 회색 셀이 포함됩니다. 모든 검정색 셀에는 2개의 AND 게이트와 단일 OR 게이트가 있고 모든 회색 셀에는 단 하나의 AND 게이트만 있습니다.

Brent-kung 가산기에는 두 단계가 포함됩니다. 전처리 단계와 생성 단계. 첫 번째 단계에서는 모든 입력 쌍에서 생성 및 전파가 수행됩니다. 여기서 전파는 입력 비트에 대해 'XOR' 연산을 제공하는 반면 생성은 입력 비트에 대해 'AND' 연산을 제공합니다. 'Pi', 'Gi'와 같은 전파 및 생성은 다음과 같습니다.

Pi = Ai XOR Bi 및 Gi = Ai AND Bi.

두 번째 단계에서는 캐리 생성 'Cg'라고 알려진 모든 비트에 대해 캐리가 생성되고 캐리 생성 'Cp'라고 알려진 모든 비트에 대해 캐리가 전파됩니다. 추가 작업을 위해 캐리 전파 및 캐리 생성이 생성됩니다. 모든 비트 연산 내에서 사용 가능한 최종 셀은 캐리를 제공합니다. 따라서 최종 비트 캐리는 마지막 비트까지 동시에 다음 비트의 합을 보조합니다. 캐리 생성 및 전파는 다음과 같이 주어진다.

Cp = P1 AND P0 및 Cg=G1 OR (P1 AND G0)

주로 2개의 32비트의 덧셈 연산에 사용되며, 모든 비트는 전처리 단계와 생성 단계를 거쳐 최종 합계를 제공합니다.

기본 입력 비트는 전처리 단계 아래로 이동하여 전파 및 생성을 생성합니다. 따라서 이러한 전파 및 생성은 생성 단계를 거쳐 캐리 생성 및 캐리 전파를 거쳐 최종 합계를 제공합니다. Brent-kung 가산기의 단계별 프로세스는 다음과 같습니다.

Brent-kung 가산기 배열은 트리 구조처럼 보이며 게이트 수준 논리를 대상으로 하는 고속 가산기입니다. 이 가산기는 논리 게이트 수를 줄여 설계할 수 있습니다. 따라서 이 아키텍처 내에서 활용되는 지연 및 메모리가 줄어듭니다.

브렌트 쿵 가산기 Verilog 코드

Brent Kung 가산기 Verilog 코드는 다음과 같습니다.

`define INPUTSIZE 64 //입력 크기 n 설정

`GROUPSIZE 8 정의 //그룹 크기 설정 = 1, 2, 4 또는 8

모듈 Brent_Kung_Adder(A, B, S);

입력 [`INPUTSIZE – 1:0] A;

입력 [`INPUTSIZE – 1:0] B;

출력 [`INPUTSIZE:0] S;

wire [`INPUTSIZE / `GROUPSIZE * 2 – 1:0] r_temp;

wire [`INPUTSIZE / `GROUPSIZE * 2 – 1:0] r;

와이어 [`INPUTSIZE / `GROUPSIZE:0] cin;

wire [`INPUTSIZE / `GROUPSIZE * 2 – 1:0] q;

cin[0] = 1'b0을 할당합니다.

생성하다

어디에;

for (i = 0; i < `INPUTSIZE / `GROUPSIZE; i = i + 1) 시작: 병렬_FA_CLA_prefix

group_q_세대 #(.Groupsize(`GROUPSIZE))

에프(

.a(A[`GROUPSIZE * (i + 1) – 1:`GROUPSIZE * i]),

.b(B[`GROUPSIZE * (i + 1) – 1:`GROUPSIZE * i]),

.cin(cin[i]),

.s(S[`GROUPSIZE * (i + 1) – 1:`GROUPSIZE * i]),

.qg(q[i * 2 + 1:i * 2])

);

끝

parallel_prefix_tree_first_half #(.Treesize(`INPUTSIZE / `GROUPSIZE))

t1(

.q(q[`입력 크기 / `그룹 크기 * 2 – 1:0]),

.r(r_temp[`INPUTSIZE / `GROUPSIZE * 2 – 1:0])

);

parallel_prefix_tree_second_half #(.Treesize(`INPUTSIZE / `GROUPSIZE))

t2(

.q(r_temp[`INPUTSIZE / `GROUPSIZE * 2 – 1:0]),

.r(r[`입력 크기 / `그룹 크기 * 2 – 1:0])

);

for (i = 0; i < `INPUTSIZE / `GROUPSIZE; i = i + 1) 시작: cin_세대

cin_세대_논리 f(

.r(r[2 * i + 1:2 * i]),

.c0(1'b0),

.cin(cin[i + 1])

);

끝

S[`INPUTSIZE] = cin[`INPUTSIZE / `GROUPSIZE] 할당;

최종 생성

엔드모듈

// 병렬 접두사 트리의 전반부

모듈parallel_prefix_tree_first_half #(매개변수 Treesize = `INPUTSIZE / `GROUPSIZE)(q, r);

입력 [Treesize * 2 – 1:0] q;

출력 [Treesize * 2 – 1:0] r;

생성하다

어디에;

if (Treesize == 2) 시작: trivial_case

r[1:0] = q[1:0] 할당;

접두사_논리 f(

.ql(q[1:0]),

.qh(q[3:2]),

.r(r[3:2])

);

끝, 그렇지 않으면 시작: recursive_case

wire [Treesize * 2 – 1:0] r_temp;

parallel_prefix_tree_first_half #(.Treesize(Treesize / 2))

recursion_lsbh(

.q(q[나무 크기 – 1:0]),

.r(r_temp[나무 크기 – 1:0])

);

parallel_prefix_tree_first_half #(.Treesize(Treesize / 2))

recursion_msbh(

.q(q[나무 크기 * 2 – 1:나무 크기]),

.r(r_temp[나무 크기 * 2 – 1:나무 크기])

);

for (i = 0; i < Treesize * 2; i = i + 2) 시작: 평행 스티치_업

if (i != Treesize * 2 – 2) 시작: 평행_스티치_업_패스

r[i + 1:i] = r_temp[i + 1:i] 할당;

끝, 그렇지 않으면 시작: 평행_스티치_업_생산

접두사_논리 f(

.ql(r_temp[나무 크기 – 1:나무 크기 – 2]),

.qh(r_temp[나무 크기 * 2 – 1:나무 크기 * 2 – 2]),

.r(r[나무 크기 * 2 – 1:나무 크기 * 2 – 2])

);

끝

끝

끝

최종 생성

엔드모듈

// 병렬 접두사 트리의 후반부

모듈parallel_prefix_tree_second_half #(매개변수 Treesize = `INPUTSIZE / `GROUPSIZE)(q, r);

입력 [Treesize * 2 – 1:0] q;

출력 [Treesize * 2 – 1:0] r;

wire [Treesize * 2 * ($clog2(Treesize) – 1) – 1:0] r_temp;

r_temp[나무 크기 * 2 – 1:0] = q[나무 크기 * 2 – 1:0] 할당;

생성하다

Genvar i, j;

for (i = 0; i < $clog2(Treesize) – 2; i = i + 1) 시작: second_half_level

r_temp[Treesize * 2 * (i + 1) + ((Treesize / (2 ** i)) – 1 – 2 ** ($clog2(Treesize / 4) – i)) * 2 – 1:Treesize * 2 할당 * (i + 1)] = r_temp[Treesize * 2 * i + ((Treesize / (2 ** i)) – 1 – 2 ** ($clog2(Treesize / 4) – i)) * 2 – 1: 트리 크기 * 2 * i];

for (j = (Treesize / (2 ** i)) – 1 – 2 ** ($clog2(Treesize / 4) – i); j < Treesize; j = j + 2 ** ($clog2(Treesize / 2 ) – i)) 시작: second_half_level_logic

접두사_논리 f(

.ql(r_temp[Treesize * 2 * i + (j – 2 ** ($clog2(Treesize / 4) – i)) * 2 + 1:Treesize * 2 * i + (j – 2 ** ($clog2( 나무 크기 / 4) – i)) * 2]),

.qh(r_temp[Treesize * 2 * i + j * 2 + 1:Treesize * 2 * i + j * 2]),

.r(r_temp[나무 크기 * 2 * (i + 1) + j * 2 + 1:나무 크기 * 2 * (i + 1) + j * 2])

);

if (j != Treesize – 1 – 2 ** ($clog2(Treesize / 4) – i)) 시작: second_half_level_direct_connect

r_temp[Treesize * 2 * (i + 1) + (j + 2 ** ($clog2(Treesize / 2) – i)) * 2 – 1:Treesize * 2 * (i + 1) + j * 2 + 2] = r_temp[Treesize * 2 * i + (j + 2 ** ($clog2(Treesize / 2) – i)) * 2 – 1:Treesize * 2 * i + j * 2 + 2];

끝

끝

r_temp[Treesize * 2 * (i + 2) – 1:Treesize * 2 * (i + 2) – (2 ** ($clog2(Treesize / 4) – i)) * 2] = r_temp[Treesize * 2 * (i + 1) – 1:Treesize * 2 * (i + 1) – (2 ** ($clog2(Treesize / 4) – i)) * 2];

끝

r[1:0] = r_temp[Treesize * 2 * ($clog2(Treesize) – 2) + 1:Treesize * 2 * ($clog2(Treesize) – 2)] 할당;

for (i = 1; i < Treesize; i = i + 2) 시작: final_r_odd

r[i * 2 + 1:i * 2] = r_temp[Treesize * 2 * ($clog2(Treesize) – 2) + i * 2 + 1:Treesize * 2 * ($clog2(Treesize) – 2) + 할당 나는 * 2];

끝

for (i = 2; i < Treesize; i = i + 2) 시작: final_r_even

접두사_논리 f(

.ql(r_temp[Treesize * 2 * ($clog2(Treesize) – 2) + i * 2 – 1:Treesize * 2 * ($clog2(Treesize) – 2) + i * 2 – 2]),

.qh(r_temp[Treesize * 2 * ($clog2(Treesize) – 2) + i * 2 + 1:Treesize * 2 * ($clog2(Treesize) – 2) + i * 2]),

“교류를 사용하는 장치 ”

.r(r[i * 2 + 1:i * 2])

);

끝

최종 생성

엔드모듈

모듈 group_q_세대 #(매개변수 Groupsize = `GROUPSIZE)(a, b, cin, s, qg);

입력 [그룹 크기 – 1:0] a;

입력 [그룹 크기 – 1:0] b;

입력 cin;

출력 [그룹 크기 - 1:0] s;

출력 [1:0] qg;

와이어 [2 * 그룹 크기 – 1:0] q;

와이어 [그룹 크기 - 1:0] c;

c[0] = cin을 할당합니다.

생성하다

어디에;

(i = 0; i < 그룹 크기; i = i + 1) 시작: 병렬_FA_CLA_prefix

FA_CLA_접두사 f(

.a(a[i]),

.b(b[i]),

.cin(c[i]),

.s(s[i]),

.q(q[i * 2 + 1:i * 2])

);

if (i != Groupsize – 1) 시작: 특수 케이스

c[i + 1] = q[i * 2 + 1] 할당 | (q[i * 2] & c[i]);

끝

끝

//그룹 크기에 따른 그룹 q 생성

if (그룹 크기 == 1) 시작: case_gs1

qg[1] = q[1] 할당;

qg[0] = q[0] 할당;

end else if (그룹 크기 == 2) 시작: case_gs2

qg[1] = q[3] 할당 | (q[1] & q[2]);

qg[0] = q[2] & q[0] 할당;

end else if (그룹 크기 == 4) 시작: case_gs4

qg[1] = q[7] 할당 | (q[5] & q[6]) | (q[3] & q[6] & q[4]) | (q[1] & q[6] & q[4] & q[2]);

qg[0] = q[6] & q[4] & q[2] & q[0] 할당;

end else if (그룹 크기 == 8) 시작: case_gs8

qg[1] = q[15] 할당 | (q[13] & q[14]) | (q[11] & q[14] & q[12]) | (q[9] & q[14] & q[12] & q[10]) | (q[7] & q[14] & q[12] & q[10] & q[8]) | (q[5] & q[14] & q[12] & q[10] & q[8] & q[6]) | (q[3] & q[14] & q[12] & q[10] & q[8] & q[6] & q[4]) | (q[1] & q[14] & q[12] & q[10] & q[8] & q[6] & q[4] & q[2]);

qg[0] = q[14] & q[12] & q[10] & q[8] & q[6] & q[4] & q[2] & q[0] 할당;

끝

최종 생성

엔드모듈

// Cin 생성 로직

모듈 cin_세대_논리(r, c0, cin);

입력 [1:0]r;

입력 c0;

출력 cin;

cin = (r[0] & c0) 할당 | r[1];

엔드모듈

// 접두사 연산의 기본 논리

모듈 prefix_logic(ql, qh, r);

입력 [1:0] ql;

입력 [1:0] qh;

출력 [1:0] r;

r[0] = qh[0] & ql[0] 할당;

r[1] = (qh[0] & ql[1]) 할당 | qh[1];

엔드모듈

// 캐리 미리보기 기능이 있는 전가산기 셀

모듈 FA_CLA_prefix(a, b, cin, s, q);

입력하다;

입력 b;

입력 cin;

출력;

출력 [1:0] q;

q[0] = a ^ b 할당;

s = q[0] ^ cin을 할당합니다;

q[1] = a & b를 할당합니다.

엔드모듈

장점

Brent Kung Adder의 장점은 다음과 같습니다.

- 이것은 결과를 얻기 위해 최소한의 회로를 사용하기 때문에 저전력 가산기입니다.

- 매우 인기 있고 널리 사용되는 가산기입니다.

- 이러한 종류의 가산기는 Kogge-Stone 가산기에 비해 더 적은 수의 모듈을 사용하여 구현할 수 있습니다.

- Brent-Kung 가산기 설계는 매우 쉽습니다.

- 이 가산기는 다른 모듈과의 연결 수가 적습니다.

- 이러한 가산기는 주로 Kogge-Stone 가산기의 단점을 해결하기 위해 제안되었습니다.

단점

그만큼 브렌트 쿵 아데의 단점 r 다음을 포함합니다.

- 이러한 가산기는 더 큰 지연을 가지며 모든 캐리 비트를 계산하려면 2 log2 n − 2 논리 레벨이 필요합니다.

- 이 가산기의 가장 큰 단점은 팬아웃(fanout)으로 인해 가산기 전체에 걸쳐 전류 전파가 분리되어 약해질 수 있다는 것입니다.

브렌트 쿵 애더 애플리케이션

Brent Kung Adder의 응용 프로그램은 다음과 같습니다.

- Brent-Kung 가산기는 파이프라인 방식으로 사용되어 조합 논리 깊이와 글리치 안정화를 줄여 전력 소비를 줄입니다.

- Brent-Kung 가산기는 i/p에서 모든 o/ps까지 뛰어난 수의 스테이지를 제공하지만 비대칭 중간 스테이지 로딩을 제공합니다.

- 이 가산기는 승수 및 기타 데이터 경로 요소 내에서 사용할 수 있습니다.

따라서 이는 브렌트 쿵 애더 개요 , 작동, 장점, 단점 및 응용 프로그램입니다. 이는 매우 효율적인 가산기이며 그 구조는 주로 고성능 산술 연산에 사용되는 트리 구조처럼 보입니다. 이 유형의 가산기는 매우 빠르며 주로 게이트 수준 논리에 중점을 둡니다. 이 가산기는 더 적은 수의 논리 게이트를 사용하여 설계되었습니다. 따라서 이 아키텍처 내에서 활용되는 메모리 및 지연이 줄어듭니다. 브렌트 쿵 애더(Brent kung adder)라고도 알려진 질문이 있습니다.