이 기사에서는 페라이트 코어 부스트 컨버터와 몇 개의 하프 브리지 MOSFET 드라이버 회로를 사용하여 릴레이가없는 솔리드 스테이트 스위치 모드 주 전압 안정기 회로를 설명합니다. 이 아이디어는 Mr. McAnthony Bernard가 요청했습니다.

기술 사양

늦게 나는보기 시작했다 전압 안정기는 유틸리티 공급을 조절하기 위해 하우스 홀드에서 사용 , 유틸리티가 낮을 때 전압을 높이고 유틸리티가 높을 때 강압.

그것은 180v, 200v, 220v, 240v 260v 등의 많은 탭으로 자동 변압기 스타일로 감겨 진 전원 변압기 (철심)를 중심으로 지어졌습니다.

릴레이의 도움으로 제어 회로는 출력에 적합한 탭을 선택합니다. 이 장치에 익숙하신 것 같습니다.

이 장치의 기능을 SMPS로 구현하려고 생각하기 시작했습니다. 릴레이를 사용하지 않고 일정한 220VAC와 50hz의 안정적인 주파수를 제공하는 이점이 있습니다.

이 메일에 개념의 블록 다이어그램을 첨부했습니다.

그 길을가는 것이 이해가된다면 당신의 생각을 알려주세요.

실제로 작동하고 동일한 목적을 수행합니까? .

또한 고전압 DC-DC 컨버터 섹션에서 귀하의 도움이 필요합니다.

문안 인사

맥 앤소니 버나드

디자인

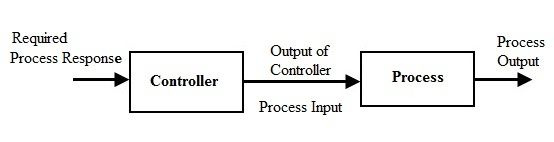

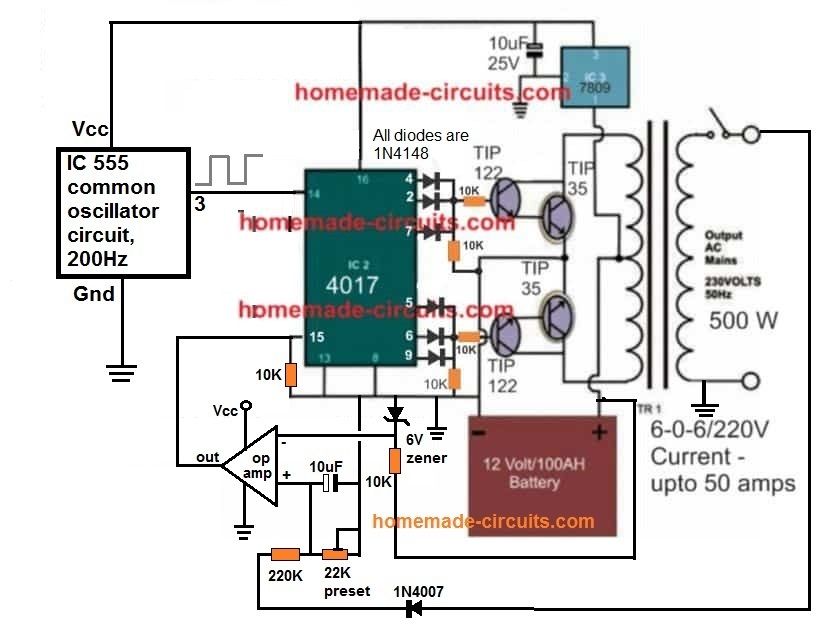

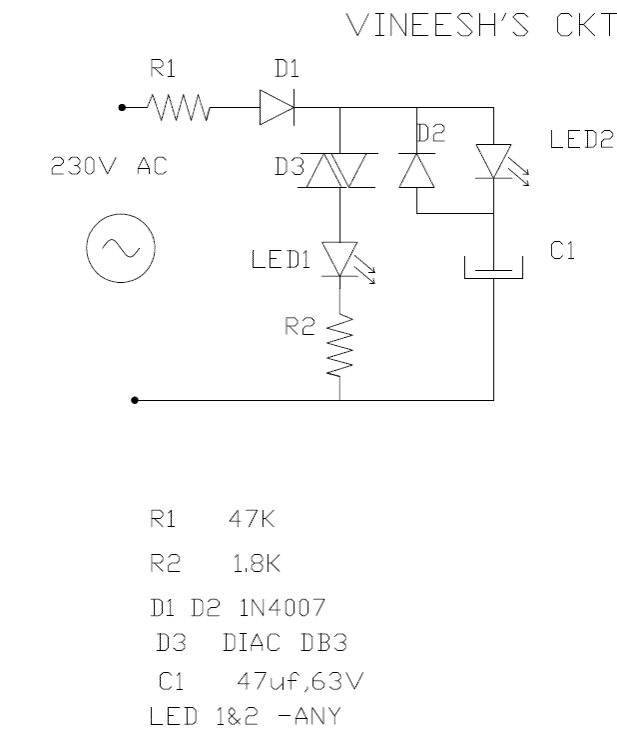

제안 된 솔리드 스테이트 페라이트 코어 기반의 릴레이없는 전원 전압 안정기 회로는 다음 다이어그램과 후속 설명을 참조하여 이해할 수 있습니다.

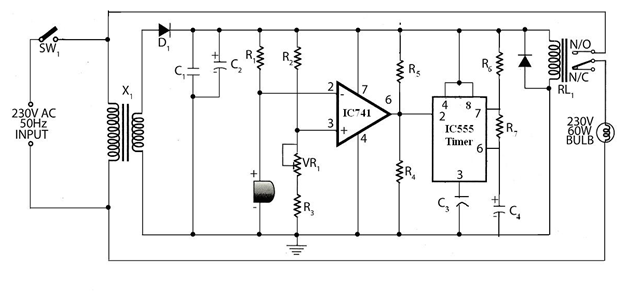

RVCC = 1K.1watt, CVCC = 0.1uF / 400V, CBOOT = 1uF / 400V

위의 그림은 두 개의 비 절연 부스트 컨버터 프로세서 스테이지를 사용하여 입력 변동이나 과부하에 관계없이 안정화 된 220V 또는 120V 출력을 구현하기위한 실제 구성을 보여줍니다.

여기서 2 개의 하프 브리지 드라이버 MOSFET IC가 전체 설계의 핵심 요소가됩니다. 관련된 IC는 복잡한 외부 회로없이 하프 브리지 모드에서 MOSFET을 구동하도록 특별히 설계된 다목적 IRS2153입니다.

두 개의 동일한 하프 브리지 드라이버 스테이지가 통합 된 것을 볼 수 있습니다. 왼쪽 드라이버는 부스트 드라이버 스테이지로 사용되고 오른쪽은 외부 전압 제어와 함께 50Hz 또는 60Hz 사인파 출력으로 부스트 전압을 처리하도록 구성됩니다. 회로.

IC는 내부적으로 프로그래밍되어 토템폴 토폴로지를 통해 출력 핀아웃에서 고정 된 50 % 듀티 사이클을 생성합니다. 이러한 핀아웃은 의도 된 변환을 구현하기 위해 전력 MOSFET과 연결됩니다. IC는 또한 출력에서 필요한 주파수를 활성화하기 위해 내부 발진기를 갖추고 있으며, 주파수 속도는 외부에서 연결된 Rt / Ct 네트워크에 의해 결정됩니다.

종료 기능 사용

IC는 또한 과전류, 과전압 또는 갑작스런 재앙 상황에서 출력을 정지시키는 데 사용할 수있는 셧다운 기능을 갖추고 있습니다.

일에 대한 자세한 정보 이다 하프 브리지 드라이버 IC 이 기사에 : 하프 브리지 MOSFET 드라이버 IC IRS2153 (1) D-핀아웃, 애플리케이션 노트 설명

이러한 IC의 출력은 연결된 장치의 완벽하고 안전한 작동을 보장하는 고도로 정교한 내부 부트 스트랩 및 데드 타임 처리로 인해 매우 균형을 이룹니다.

논의 된 SMPS 전원 전압 안정기 회로에서 왼쪽 스테이지는 전원 220V 입력을 정류하여 파생 된 310V 입력에서 약 400V를 생성하는 데 사용됩니다.

120V 입력의 경우 표시된 인덕터를 통해 약 200V를 생성하도록 스테이지를 설정할 수 있습니다.

인덕터는 0.3mm 수퍼 에나멜 구리 와이어의 3 개의 병렬 (바이 필러) 스트랜드를 사용하여 표준 EE 코어 / 보빈 어셈블리 위에 감을 수 있으며 약 400 회 회전 할 수 있습니다.

주파수 선택

주파수는 Rt / Ct의 값을 올바르게 선택하여 설정해야합니다. 그러면 표시된 인덕터에서 왼쪽 부스트 컨버터 단계에 대해 약 70kHz의 고주파가 달성됩니다.

오른쪽 드라이버 IC는 다이어그램에서 볼 수 있듯이 적절한 정류 및 여과 후 부스트 컨버터의 400V DC 이상에서 작동하도록 배치됩니다.

여기서 Rt 및 Ct 값은 연결된 MOSFET 출력에서 약 50Hz 또는 60Hz (국가 사양에 따라)를 획득하도록 선택됩니다.

그러나 오른쪽 드라이버 스테이지의 출력은 550V까지 높을 수 있으며, 이는 약 220V 또는 120V에서 원하는 안전 수준으로 조정되어야합니다.

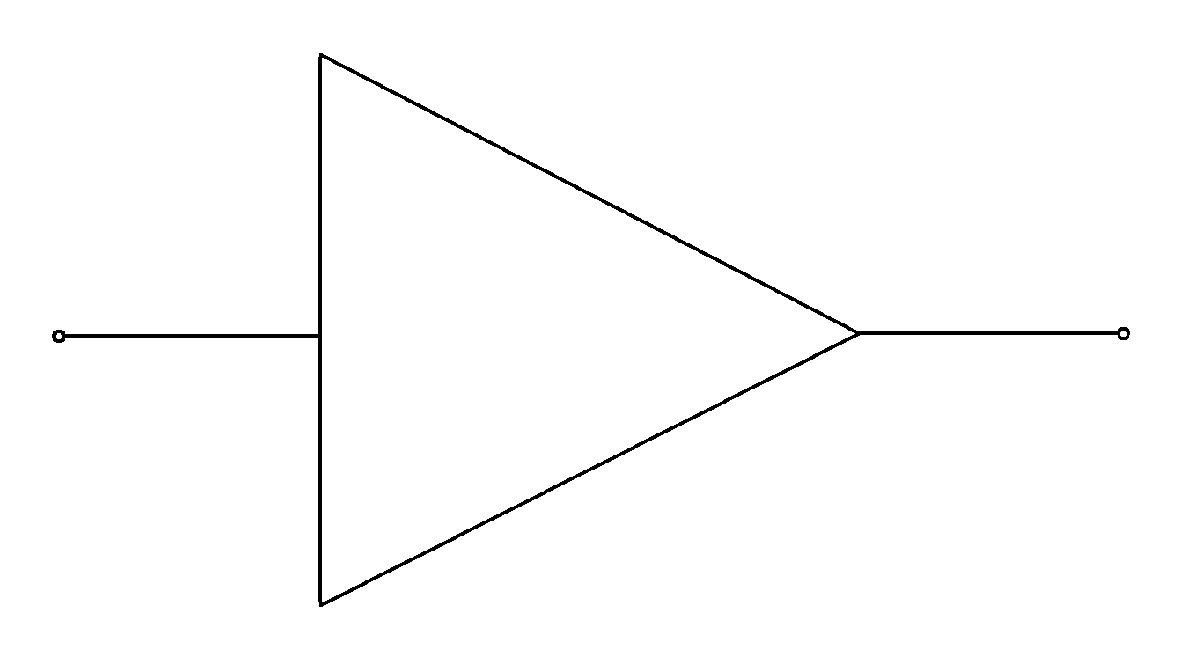

이를 위해 다음 다이어그램과 같이 간단한 opamp 오류 증폭기 구성이 포함됩니다.

과전압 보정 회로

위의 다이어그램에서 볼 수 있듯이 전압 보정 단계는 과전압 상태를 감지하기 위해 간단한 opamp 비교기를 사용합니다.

회로는 입력 변동이나 과부하에 관계없이 설정된 수준에서 영구적으로 안정화 된 전압을 즐기기 위해 한 번만 설정하면되지만, 설계의 지정된 허용 한계를 초과 할 수 없습니다.

그림과 같이 오류 증폭기에 대한 공급은 AC를 회로에 대해 깨끗한 저 전류 안정화 12V DC로 적절하게 정류 한 후 출력에서 파생됩니다.

핀 # 2는 IC의 센서 입력으로 지정되고 비 반전 핀 # 3은 클램핑 제너 다이오드 네트워크를 통해 고정 된 4.7V를 참조합니다.

감지 입력은 회로의 불안정한 지점에서 추출되고 IC의 출력은 오른쪽 드라이버 IC의 Ct 핀에 연결됩니다.

이 핀은 IC의 셧다운 핀 역할을하며 Vcc의 1/6 미만이 낮아지면 즉시 MOSFET에 대한 출력 피드를 차단하여 진행을 중단합니다.

opamp의 핀 # 2와 관련된 사전 설정은 출력 주전원 AC가 사용 가능한 450V 또는 500V 출력에서 220V로, 250V 출력에서 120V로 안정되도록 적절하게 조정됩니다.

핀 # 2가 핀 # 3과 관련하여 더 높은 전압을 경험하는 한, 출력을 계속 낮게 유지하여 차례로 드라이버 IC를 종료하도록 명령하지만 '종료'는 즉시 opamp 입력을 수정하여 강제합니다. 출력 로우 신호를 철회하고 사이클은 핀 # 2 사전 설정에 의해 결정된 정확한 레벨로 출력을 자체 수정합니다.

오류 증폭기 회로는이 출력을 계속 안정화하고 회로가 입력 소스 전압과 조정 된 전압 값 사이에 100 % 여유가 있다는 장점이 있기 때문에 매우 낮은 전압 조건에서도 출력이 부하에 고정 된 안정화 전압을 제공하도록 관리합니다. 전압에 관계없이 일치하지 않는 부하 또는 과부하가 출력에 연결된 경우에도 마찬가지입니다.

위의 디자인 개선 :

주의 깊게 조사한 결과 위의 디자인은 효율성과 출력 품질을 높이기 위해 크게 수정하고 개선 할 수 있습니다.

- 인덕터는 실제로 필요하지 않으며 제거 할 수 있습니다.

- 전력이 부하에 최적이되도록 출력을 풀 브리지 회로로 업그레이드해야합니다.

- 출력은 위 설계에서 예상 할 수있는 수정 된 것이 아니라 순수 사인파 여야합니다.

이러한 모든 기능은 솔리드 스테이트 스태빌라이저 회로의 다음 업그레이드 버전에서 고려되고 처리되었습니다.

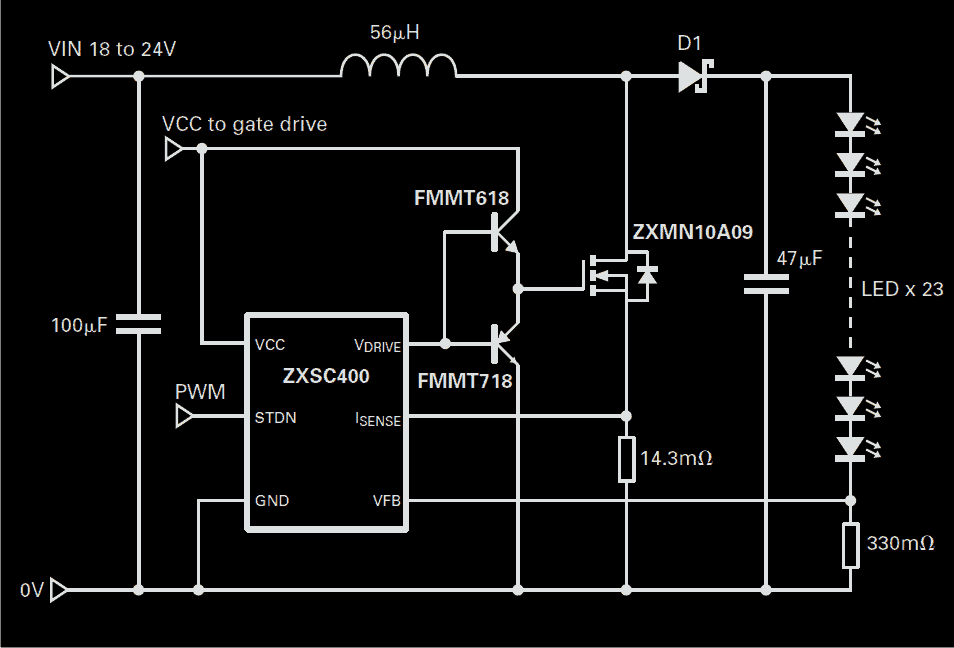

회로 작동

- IC1은 R1의 값을 적절히 변경하여 주파수를 조정할 수있는 일반적인 불안정한 멀티 바이브레이터 발진기 회로처럼 작동합니다. 이것은 SPWM 출력에 대한 '기둥'또는 '잘라 내기'의 수를 결정합니다.

- 핀 # 3에서 IC 1의 주파수는 PWM 생성기로 연결된 IC2의 핀 # 2로 공급됩니다.

- 이 주파수는 IC2의 6 번 핀에서 삼각파로 변환되며 IC2의 5 번 핀의 샘플 전압과 비교됩니다.

- IC2의 5 번 핀은 브리지 정류기에서 획득 한 100Hz 주파수의 샘플 사인파와 함께 적용되며, 전원을 12V로 적절하게 낮추었습니다.

- 이러한 사인파 샘플은 IC2의 핀 # 7 삼각파와 비교되어 IC2의 핀 # 3에서 비례 적으로 작은 크기의 SPWM이 생성됩니다.

- 이제이 SPWM의 펄스 폭은 브리지 정류기의 샘플 사인파 진폭에 따라 달라집니다. 즉, AC 주전원 전압이 높으면 더 넓은 SPWM이 생성되고 AC 주전원 전압이 낮 으면 SPWM 폭이 줄어들고 비례 적으로 더 좁아집니다.

- 위의 SPWM은 BC547 트랜지스터에 의해 반전되고 풀 브리지 드라이버 네트워크의 로우 사이드 MOSFET의 게이트에 적용됩니다.

- 이것은 AC 주전원 레벨이 떨어지면 MOSFET 게이트의 응답이 비례 적으로 더 넓은 SPWM의 형태가되고 AC 주전원 전압이 증가하면 게이트가 비례 적으로 저하되는 SPWM을 경험하게된다는 것을 의미합니다.

- 위의 애플리케이션은 입력 AC 주전원이 떨어질 때마다 H- 브리지 네트워크 사이에 연결된 부하에 비례적인 전압 부스트를 발생시키고 반대로 AC가 위험 수준 이상으로 상승하는 경향이있는 경우 부하가 비례적인 양의 전압 강하를 거치게됩니다.

회로 설정 방법

SPWM 응답이 주 AC 레벨과 동일 할 수있는 대략적인 중앙 전환 지점을 결정합니다.

220V로 선택한 다음 H 브리지에 연결된 부하가 약 220V를 수신하도록 1K 사전 설정을 조정한다고 가정합니다.

이제 설정이 완료되었으며 나머지는 자동으로 처리됩니다.

또는 동일한 방식으로 위의 설정을 낮은 전압 임계 값 수준으로 수정할 수 있습니다.

하한 임계 값이 170V라고 가정하면이 경우 170V를 회로에 공급하고 부하 전체 또는 H- 브리지 암 사이에서 약 210V를 찾을 때까지 1K 사전 설정을 조정합니다.

이 단계는 설정 절차를 마치고 나머지는 입력 AC 레벨 변경에 따라 자동으로 조정됩니다.

중대한 : H- 브리지 네트워크에 공급되는 AC 정류 라인에 500uF / 400V 순으로 고가 커패시터를 연결하여 정류 된 DC가 H- 브리지 BUS 라인을 통해 최대 310V DC에 도달 할 수 있도록하십시오.

이전 : 다이오드 및 트랜지스터로 3.3V, 5V 전압 조정기 회로 만들기 다음 : 간단한 뮤지컬 도어 벨 회로