이 포스트에서 우리는 논리 게이트가 무엇인지 그리고 그 작동에 대해 포괄적으로 이해할 것입니다. 기본 정의, 기호, 진리표, 다중 입력 게이트를 살펴보고 트랜지스터 기반 게이트 등가물을 구성하고 마지막으로 다양한 관련 CMOS IC에 대한 개요를 살펴 보겠습니다.

논리 게이트는 무엇입니까

전자 회로의 논리 게이트는 Boolean 함수를 통해 표현되는 물리적 단위로 표현할 수 있습니다.

즉, 논리 게이트는 하나 이상의 이진 입력을 사용하여 논리 함수를 실행하고 단일 이진 출력을 생성하도록 설계되었습니다.

전자 로직 게이트는 잘 정의 된 스위칭 패턴을 가진 ON / OFF 스위치처럼 작동하는 다이오드 또는 트랜지스터와 같은 반도체 블록 또는 요소를 사용하여 기본적으로 구성 및 구현됩니다. 논리 게이트는 게이트의 계단식 연결을 용이하게하여 부울 함수를 쉽게 구성 할 수 있도록하여 모든 부울 논리의 물리적 모델을 생성 할 수 있습니다. 이것은 또한 부울 논리를 사용하여 쓸 수있는 알고리즘과 수학을 가능하게합니다.

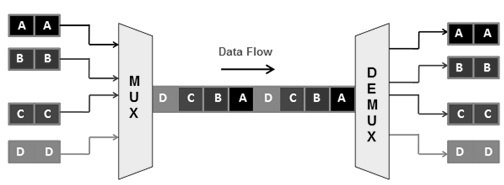

논리 회로는 멀티플렉서, 레지스터, ALU (산술 논리 장치) 및 컴퓨터 메모리 범위의 반도체 요소를 사용할 수 있으며 최대 수억 개의 논리 게이트를 포함하는 마이크로 프로세서까지 사용할 수 있습니다. 오늘날의 구현에서는 로직 게이트 제조에 사용되는 전계 효과 트랜지스터 (FET)를 대부분 찾을 수 있습니다. 좋은 예로 금속 산화물 반도체 전계 효과 트랜지스터 또는 MOSFET이 있습니다.

논리 AND 게이트로 튜토리얼을 시작하겠습니다.

로직 'AND'게이트는 무엇입니까?

이는 전자 게이트로, AND 게이트의 모든 입력이 '하이'또는 '1'또는 '참'또는 ''일 때 '출력이'high '또는'1 '또는'true '로 바뀌거나'positive signal '을 제공합니다. 긍정적 인 신호”.

예 : 입력 수가 'n'인 AND 게이트에서 모든 입력이 '높음'이면 출력이 '높음'으로 바뀝니다. 한 입력이 'LOW', '0'또는 'false'또는 'negative signal'인 경우에도 출력은 'LOW'또는 '0'또는 'false'로 바뀌거나 'negative signal'을 제공합니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리 AND 게이트 기호 그림 :

여기서 'A'와 'B'는 두 개의 입력이고 'Y'는 출력입니다.

논리 AND 게이트의 부울 표현식 : 출력‘Y’는 두 입력‘A’와‘B’의 곱셈입니다. (A.B) = Y.

부울 곱셈은 점 (.)으로 표시됩니다.

‘A’가‘1’이고‘B’가‘1’이면 출력은 (A.B) = 1 x 1 =‘1’또는“high”입니다.

‘A’가‘0’이고‘B’가‘1’이면 출력은 (A.B) = 0 x 1 =‘0’또는“낮음”입니다.

‘A’가‘1’이고‘B’가‘0’이면 출력은 (A.B) = 1 x 0 =‘0’또는“Low”입니다.

‘A’가‘0’이고‘B’가‘0’이면 출력은 (A.B) = 0 x 0 =‘0’또는 '낮음'입니다.

위의 조건은 진리표에서 단순화되었습니다.

진리표 (두 입력) :

| A (입력) | B (입력) | Y (출력) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3- 입력 'AND'게이트 :

3 개의 입력 AND 게이트 그림 :

논리 AND 게이트는 'n'개의 입력을 가질 수 있습니다. 즉, 2 개 이상의 입력을 가질 수 있습니다 (논리 AND 게이트는 입력이 최소 2 개이고 항상 출력이 1 개임).

3 입력 AND 게이트의 경우 부울 방정식은 다음과 같이 바뀝니다. (A.B.C) = Y, 4 입력 이상에 대해서도 유사합니다.

3 개의 입력 로직 및 게이트에 대한 진리표 :

| A (입력) | B (입력) | C (입력) | Y (출력) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

다중 입력 로직 및 게이트 :

상업적으로 사용 가능한 로직 AND 게이트는 2, 3 및 4 입력에서만 사용할 수 있습니다. 입력이 4 개 이상이면 게이트를 계단식으로 연결해야합니다.

다음과 같이 2 개의 입력 AND 게이트를 계단식으로 연결하여 6 개의 입력 논리 AND 게이트를 가질 수 있습니다.

이제 위 회로의 부울 방정식은 Y = (A.B). (C.D). (E.F)가됩니다.

그래도 언급 된 모든 논리적 규칙은 위의 회로에 적용됩니다.

위의 6 개 입력 AND 게이트에서 5 개의 입력 만 사용하려는 경우 한 핀에 풀업 저항을 연결할 수 있으며 이제 5 개 입력 AND 게이트가됩니다.

트랜지스터 기반 2 개의 입력 논리 AND 게이트 :

이제 논리 AND 게이트가 어떻게 작동하는지 알았습니다. 두 개의 NPN 트랜지스터를 사용하여 2 개의 입력 AND 게이트를 구성 해 보겠습니다. 로직 IC는 거의 동일한 방식으로 구성됩니다.

2 개의 트랜지스터 및 게이트 회로도 :

출력 'Y'에서 LED를 연결할 수 있습니다. 출력이 높으면 LED가 켜집니다 (LED + Ve 단자는 'Y'에 330ohm 저항이 있고 음은 GND에 있음).

두 트랜지스터의베이스에 높은 신호를 적용하면 두 트랜지스터가 모두 켜지고 T2의 이미 터에서 + 5V 신호를 사용할 수 있으므로 출력이 높아집니다.

트랜지스터 중 하나가 꺼져 있으면 T2의 이미 터에서 양의 전압을 사용할 수 없지만 1K 풀다운 저항으로 인해 출력에서 음의 전압을 사용할 수 있으므로 출력을 낮음이라고합니다.

이제 논리와 게이트를 직접 구성하는 방법을 알았습니다.

쿼드 AND 게이트 IC 7408 :

시장에서 로직 및 게이트를 구매하려면 위의 구성을 사용하게됩니다.

핀 # 7과 핀 # 14는 각각 GND와 Vcc 인 14 개의 핀을 가지고 있습니다. 5V에서 작동합니다.

전파 지연 :

전파 지연은 출력이 LOW에서 HIGH로 또는 그 반대로 변경되는 데 걸리는 시간입니다.

LOW에서 HIGH 로의 전파 지연은 27 나노초입니다.

HIGH에서 LOW 로의 전파 지연은 19 나노초입니다.

기타 일반적으로 사용 가능한 'AND'게이트 IC :

• 74LS08 쿼드 2 입력

• 74LS11 트리플 3 입력

• 74LS21 듀얼 4 입력

• CD4081 쿼드 2 입력

• CD4073 트리플 3 입력

• CD4082 듀얼 4 입력

자세한 내용은 항상 위 IC에 대한 데이터 시트를 참조 할 수 있습니다.

논리 '독점적 NOR'게이트 기능

이 게시물에서는 논리 'Ex-NOR'게이트 또는 Exclusive-NOR 게이트에 대해 살펴 보겠습니다. 기본 정의, 기호, 진리표, Ex-NOR 등가 회로, Ex-NOR를 이용한 Ex-NOR 구현을 살펴 보겠습니다. 논리 NAND 게이트 마지막으로 쿼드 2 입력 Ex-OR 게이트 IC 74266에 대한 개요를 살펴 보겠습니다.

“독점 NOR”게이트는 무엇입니까?

입력이 논리 '1'(또는 '참'또는 '높음'또는 '')의 짝수 일 때 출력이 'high'또는 '1'또는 'true'로 바뀌거나 'positive signal'을 출력하는 전자 게이트입니다. 긍정적 인 신호”).

예를 들어, 'n'개의 입력이있는 Exclusive NOR 게이트를 말하면, 입력이 2 개 또는 4 개 또는 6 개의 입력 (짝수 입력 '1s')이있는 논리 'HIGH'이면 출력이 'HIGH'가됩니다.

입력 핀에 로직 '하이'를 적용하지 않더라도 (즉, 로직 'HIGH'의 수는 0이고 모든 로직은 'LOW'), 여전히 '0'은 출력이 'HIGH'가되는 짝수입니다.

적용된 논리 '1'의 수가 ODD이면 출력이 'LOW'(또는 '0', 'false'또는 'negative signal')가됩니다.

이것은 입력이 논리 '1s'의 ODD 수일 때 출력이 'HIGH'가되는 논리 'Exclusive OR'게이트와 반대입니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리 '배타적 NOR'게이트 그림 :

'독점 NOR'게이트 등가 회로 :

위는 논리 Ex-NOR의 등가 회로로, 기본적으로 논리“Exclusive OR”게이트와 논리“NOT”게이트의 조합입니다.

여기서 'A'와 'B'는 두 개의 입력이고 'Y'는 출력입니다.

논리 Ex-NOR 게이트에 대한 부울 식 : Y = (AB) ̅ + AB.

‘A’가‘1’이고‘B’가‘1’이면 출력은 ((AB) ̅ + AB) = 0 + 1 =‘1’또는“HIGH”입니다.

‘A’가‘0’이고‘B’가‘1’이면 출력은 ((AB) ̅ + AB) = 0 + 0 =‘0’또는“LOW”입니다.

‘A’가‘1’이고‘B’가‘0’이면 출력은 ((AB) ̅ + AB) = 0 + 0 =‘0’또는“LOW”입니다.

‘A’가‘0’이고‘B’가‘0’이면 출력은 ((AB) ̅ + AB) = 1 + 1 =‘1’또는“HIGH”입니다.

위의 조건은 진리표에서 단순화되었습니다.

진리표 (두 입력) :

| A (입력) | B (입력) | Y (출력) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3 입력 전용 NOR 게이트 :

3 개의 입력 Ex-NOR 게이트 그림 :

3 개의 입력 로직 EX-OR 게이트에 대한 진리표 :

| A (입력) | B (입력) | C (입력) | Y (출력) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

3 입력 Ex-NOR 게이트의 경우 부울 방정식은 A̅ (BC) ̅ + ABC̅ + AB̅C + A̅BC가됩니다.

로직 'Ex-NOR'게이트는 기본 로직 게이트가 아니라 서로 다른 로직 게이트의 조합입니다. Ex-NOR 게이트는 논리 'OR'게이트, 논리 'AND'게이트 및 논리 'NAND'게이트를 사용하여 다음과 같이 구현할 수 있습니다.

'독점 NOR'게이트의 등가 회로 :

위의 설계에는 큰 단점이 있습니다. 하나의 Ex-NOR 게이트를 만들려면 3 개의 다른 논리 게이트가 필요합니다. 그러나 로직 'NAND'게이트만으로 Ex-NOR 게이트를 구현하여이 문제를 극복 할 수 있으며, 이는 또한 제작하기에 경제적입니다.

NAND 게이트를 사용하는 독점 NOR 게이트 :

독점 NOR 게이트는 산술 연산, 이진 가산기, 이진 빼기, 패리티 검사기와 같은 복잡한 컴퓨팅 작업을 수행하는 데 사용되며 디지털 비교기로 사용됩니다.

논리 배타적 NOR 게이트 IC 74266 :

시장에서 로직 Ex-NOR 게이트를 구매하려는 경우 위의 DIP 구성이 제공됩니다.

핀 # 7과 핀 # 14는 각각 GND와 Vcc 인 14 개의 핀을 가지고 있습니다. 5V에서 작동합니다.

전파 지연 :

전파 지연은 입력을 제공 한 후 출력이 LOW에서 HIGH로 또는 그 반대로 변경되는 데 걸리는 시간입니다.

LOW에서 HIGH 로의 전파 지연은 23 나노초입니다.

HIGH에서 LOW 로의 전파 지연은 23 나노초입니다.

일반적으로 사용 가능한 'EX-NOR'게이트 IC :

74LS266 쿼드 2 입력

CD4077 쿼드 2 입력

NAND Gate의 작동 원리

아래 설명에서 우리는 디지털 로직 NAND 게이트에 대해 살펴볼 것입니다. 기본 정의, 기호, 진리표, 다중 입력 NAND 게이트를 살펴보고, 트랜지스터 기반의 2 입력 NAND 게이트, NAND 게이트만을 사용하는 다양한 로직 게이트를 구성하고 마지막으로 NAND 게이트에 대해 살펴 보겠습니다. IC 7400.

로직 'NAND'게이트는 무엇입니까?

NAND 게이트의 모든 입력이 '높음', '1'또는 '참'또는 ''일 때 출력이 'LOW'또는 '0'또는 'false'로 바뀌거나 '부정 신호'를내는 전자 게이트입니다. 긍정적 인 신호”.

예 : 'n'개의 입력이있는 NAND 게이트를 말하면 모든 입력이 '높음'이면 출력이 '낮음'으로 바뀝니다. 한 입력이 'LOW', '0'또는 'false'또는 'negative signal'인 경우에도 출력은 'HIGH'또는 '1'또는 'true'로 바뀌거나 'positive signal'을 제공합니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리 NAND 게이트 기호 그림 :

여기서 'A'와 'B'는 두 개의 입력이고 'Y'는 출력입니다.

이 기호는 반전 'o'가있는 'AND'게이트입니다.

논리 'NAND'게이트 등가 회로 :

논리 NAND 게이트는 논리 'AND'게이트와 논리 'NOT'게이트의 조합입니다.

논리 NAND 게이트에 대한 부울 표현식 : 출력 'Y'는 두 입력 'A'와 'B'의 보완 곱셈입니다. Y = ((A.B) ̅)

부울 곱셈은 점 (.)으로 표시되고 보완 (반전)은 문자 위에 막대 (-)로 표시됩니다.

‘A’가‘1’이고‘B’가‘1’이면 출력은 ((A.B) ̅) = (1 x 1) ̅ =‘0’또는“LOW”입니다.

‘A’가‘0’이고‘B’가‘1’이면 출력은 ((A.B) ̅) = (0 x 1) ̅ =‘1’또는“HIGH”입니다.

‘A’가‘1’이고‘B’가‘0’이면 출력은 ((A.B) ̅) = (1 x 0) ̅ =‘1’또는“HIGH”입니다.

‘A’가‘0’이고‘B’가‘0’이면 출력은 ((A.B) ̅) = (0 x 0) ̅ =‘1’또는“HIGH”입니다.

위의 조건은 진리표에서 단순화되었습니다.

진리표 (두 입력) :

| A (입력) | B (입력) | Y (출력) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

3- 입력 'NAND'게이트 :

3 개의 입력 NAND 게이트 그림 :

논리 NAND 게이트는 'n'개의 입력을 가질 수 있습니다. 즉, 2 개 이상의 입력을 가질 수 있습니다.

(로직 NAND 게이트는 최소 2 개의 입력과 항상 1 개의 출력을 갖습니다.)

3 입력 NAND 게이트의 경우 부울 방정식은 다음과 같이 바뀝니다. ((A.B.C) ̅) = Y, 4 입력 이상과 유사합니다.

진실 테이블3 개의 입력 논리 NAND 게이트의 경우 :

| A (입력) | B (입력) | C (입력) | Y (출력) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

다중 입력 논리 NAND 게이트 :

시판되는 Logic NAND 게이트는 2, 3 및 4 입력에서만 사용할 수 있습니다. 입력이 4 개 이상이면 게이트를 계단식으로 연결해야합니다.

예를 들어, 다음과 같이 5 개의 2 개의 입력 NAND 게이트를 계단식으로 연결하여 4 개의 입력 논리 NAND 게이트를 가질 수 있습니다.

이제 위 회로의 부울 방정식은 Y = ((A.B.C.D) ̅)가됩니다.

그래도 언급 된 모든 논리적 규칙은 위의 회로에 적용됩니다.

위의 4 개 입력 NAND 게이트에서 3 개의 입력 만 사용하려는 경우 풀업 저항을 임의의 핀에 연결할 수 있으며 이제 3 개의 입력 NAND 게이트가됩니다.

트랜지스터 기반 2 개의 입력 논리 NAND 게이트 :

이제 논리 NAND 게이트가 어떻게 작동하는지 알았습니다. 2 개를 사용하여 2 입력 NAND 게이트를 구성 해 보겠습니다.

NPN 트랜지스터. 로직 IC는 거의 동일한 방식으로 구성됩니다.

2 개의 트랜지스터 NAND 게이트 회로도 :

출력 'Y'에서 출력이 높으면 LED를 연결할 수 있습니다. LED가 켜집니다 (LED + Ve 단자는 330ohm 저항으로 'Y'에 있고 GND에 음수).

두 트랜지스터의베이스에 하이 신호를 적용하면 두 트랜지스터가 모두 켜지고 접지 신호가 T1의 콜렉터에서 사용 가능하므로 출력이 'LOW'가됩니다.

트랜지스터 중 하나가 꺼져있는 경우 즉, 'LOW'신호를베이스에 적용하면 T1의 콜렉터에서 접지 신호를 사용할 수 없지만 1K 풀업 저항으로 인해 양의 신호가 출력에서 사용 가능하고 출력이 회전합니다. '높은'.

이제 논리 NAND 게이트를 직접 구성하는 방법을 알았습니다.

NAND 게이트를 사용하는 다양한 로직 게이트 :

NAND 게이트는이 단일 게이트로 모든 부울 로직을 만들 수 있기 때문에 '유니버설 로직 게이트'라고도합니다. 이것은 논리 기능이 다른 IC를 제작할 때의 장점이며 단일 게이트를 제작하는 것이 경제적입니다.

위의 회로도에는 3 가지 유형의 게이트 만 표시되어 있지만 모든 부울 논리를 만들 수 있습니다.

쿼드 NAND 게이트 IC 7400 :

시장에서 논리 NAND 게이트를 구입하려면 위의 DIP 구성을 얻을 수 있습니다.

핀 # 7과 핀 # 14는 각각 GND와 Vcc 인 14 개의 핀을 가지고 있습니다. 5V에서 작동합니다.

전파 지연 :

전파 지연은 입력을 제공 한 후 출력이 LOW에서 HIGH로 또는 그 반대로 변경되는 데 걸리는 시간입니다.

LOW에서 HIGH 로의 전파 지연은 22 나노초입니다.

HIGH에서 LOW 로의 전파 지연은 15 나노초입니다.

몇 가지 다른 NAND 게이트 IC를 사용할 수 있습니다.

- 74LS00 쿼드 2 입력

- 74LS10 트리플 3 입력

- 74LS20 듀얼 4 입력

- 74LS30 단일 8 입력

- CD4011 쿼드 2 입력

- CD4023 트리플 3 입력

- CD4012 듀얼 4 입력

NOR Gate의 작동 원리

여기서 우리는 디지털 로직 NOR 게이트에 대해 알아볼 것입니다. 기본 정의, 기호, 진리표, 다중 입력 NOR 게이트를 살펴보고, 트랜지스터 기반의 2 입력 NOR 게이트, NOR 게이트 만 사용하는 다양한 로직 게이트를 구성하고 마지막으로 NOR 게이트에 대해 살펴 보겠습니다. IC 7402.

로직 'NOR'게이트는 무엇입니까?

NOR 게이트의 모든 입력이 'LOW'또는 '0'또는 'false'또는 '일 때 출력이'HIGH '또는'1 '또는'true '로 바뀌거나'positive signal '을내는 전자 게이트입니다. 부정적인 신호”.

예 : 'n'개의 입력이있는 NOR 게이트를 말하면 모든 입력이 'LOW'이면 출력이 'HIGH'가됩니다. 한 입력이 'HIGH', '1'또는 'true'또는 'positive signal'인 경우에도 출력은 'LOW'또는 '0'또는 'false'로 바뀌거나 'negative signal'을 제공합니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리 NOR 게이트 기호 그림 :

여기서 'A'와 'B'는 두 개의 입력이고 'Y'는 출력입니다.

이 기호는 반전 'o'가있는 'OR'게이트입니다.

논리 'NOR'게이트 등가 회로 :

논리 NOR 게이트는 논리 'OR'게이트와 논리 'NOT'게이트의 조합입니다.

논리 NOR 게이트의 부울 표현식 : 출력 'Y'는 두 입력 'A'와 'B'의 보완 추가입니다. Y = ((A + B) ̅)

부울 더하기는 (+)로 표시되고 보완 (반전)은 문자 위에 막대 (-)로 표시됩니다.

‘A’가‘1’이고‘B’가‘1’이면 출력은 ((A + B) ̅) = (1+ 1) ̅ =‘0’또는“LOW”입니다.

‘A’가‘0’이고‘B’가‘1’이면 출력은 ((A + B) ̅) = (0+ 1) ̅ =‘0’또는“LOW”입니다.

‘A’가‘1’이고‘B’가‘0’이면 출력은 ((A + B) ̅) = (1+ 0) ̅ =‘0’또는“LOW”입니다.

‘A’가‘0’이고‘B’가‘0’이면 출력은 ((A + B) ̅) = (0+ 0) ̅ =‘1’또는“HIGH”입니다.

위의 조건은 진리표에서 단순화되었습니다.

진리표 (두 입력) :

| A (입력) | B (입력) | Y (출력) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

3- 입력 'NOR'게이트 :

3 개의 입력 NOR 게이트 그림 :

논리 NOR 게이트는 'n'개의 입력을 가질 수 있습니다. 즉, 2 개 이상의 입력을 가질 수 있습니다 (로직 NOR 게이트에는 최소 2 개의 입력과 항상 1 개의 출력이 있음).

3 입력 NOR 게이트의 경우 부울 방정식은 다음과 같이 바뀝니다. ((A + B + C) ̅) = Y, 4 입력 이상에 대해서도 유사합니다.

3 개의 입력 논리 NOR 게이트에 대한 진리표 :

| A (입력) | B (입력) | C (입력) | Y (출력) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

다중 입력 로직 NOR 게이트 :

시판되는 Logic NOR 게이트는 2, 3 및 4 입력에서만 사용할 수 있습니다. 입력이 4 개 이상이면 게이트를 계단식으로 연결해야합니다.

예를 들어, 다음과 같이 5 개의 2 개의 입력 NOR 게이트를 계단식으로 연결하여 4 개의 입력 논리 NOR 게이트를 가질 수 있습니다.

이제 위 회로의 부울 방정식은 Y = ((A + B + C + D) ̅)가됩니다.

그래도 언급 된 모든 논리적 규칙은 위의 회로에 적용됩니다.

위의 4 개 입력 NOR 게이트에서 3 개의 입력 만 사용하려는 경우 풀다운 저항을 핀 중 하나에 연결할 수 있으며 이제 3 개의 입력 NOR 게이트가됩니다.

트랜지스터 기반 2 개의 입력 논리 NOR 게이트 :

이제 논리 NOR 게이트가 어떻게 작동하는지 알았습니다. 두 개의 NPN 트랜지스터를 사용하여 2 개의 입력 NOR 게이트를 구성 해 보겠습니다. 로직 IC는 거의 동일한 방식으로 구성됩니다.

2 개의 트랜지스터 NOR 게이트 회로도 :

출력 'Y'에서 출력이 높으면 LED를 연결할 수 있습니다. LED가 켜집니다 (LED + Ve 단자는 330ohm 저항으로 'Y'에 있고 GND에 음수).

두 트랜지스터의베이스에 'HIGH'신호를 적용하면 두 트랜지스터가 모두 켜지고 접지 신호가 T1 및 T2의 콜렉터에서 사용 가능하므로 출력이 'LOW'가됩니다.

트랜지스터 중 하나에 'HIGH'를 적용하면 여전히 출력에서 음의 신호를 사용할 수 있으므로 출력이 'LOW'가됩니다.

두 트랜지스터의베이스에 'LOW'신호를 적용하면 둘 다 꺼지지 만 풀업 저항으로 인해 출력이 'HIGH'가됩니다.

이제 논리 NOR 게이트를 직접 구성하는 방법을 알았습니다.

NOR 게이트를 사용하는 다양한 로직 게이트 :

참고 : NAND 및 NOR은 범용 게이트로 알려진 두 개의 게이트입니다.

NOR 게이트는 또한이 단일 게이트로 모든 부울 논리를 만들 수 있기 때문에 '범용 논리 게이트'입니다. 이는 논리 기능이 다른 IC를 제작할 때의 장점이며 단일 게이트를 제작하는 것이 경제적이며 NAND 게이트도 마찬가지입니다.

위의 회로도에는 3 가지 유형의 게이트 만 표시되어 있지만 모든 부울 논리를 만들 수 있습니다.

쿼드 NOR 게이트 IC 7402 :

시장에서 논리 NOR 게이트를 구입하려면 위의 DIP 구성을 얻을 수 있습니다.

핀 # 7과 핀 # 14는 각각 GND와 Vcc 인 14 개의 핀을 가지고 있습니다. 5V에서 작동합니다.

전파 지연 :

전파 지연은 입력을 제공 한 후 출력이 LOW에서 HIGH로 또는 그 반대로 변경되는 데 걸리는 시간입니다.

LOW에서 HIGH 로의 전파 지연은 22 나노초입니다.

HIGH에서 LOW 로의 전파 지연은 15 나노초입니다.

몇 가지 다른 NOR 게이트 IC를 사용할 수 있습니다.

- 74LS02 쿼드 2 입력

- 74LS27 트리플 3 입력

- 74LS260 듀얼 4 입력

- CD4001 쿼드 2 입력

- CD4025 트리플 3 입력

- CD4002 듀얼 4 입력

논리 NOT 게이트

이 게시물에서는 논리 'NOT'게이트에 대해 살펴 보겠습니다. 기본 정의, 기호, 진리표, NAND 및 NOR 게이트 등가물, Schmitt 인버터, Schmitt NOT 게이트 발진기, 트랜지스터를 사용하는 NOT 게이트에 대해 배우고 마지막으로 논리 NOT 게이트 인버터 IC 7404를 살펴볼 것입니다.

디지털 인버터라고도하는 논리 NOT 게이트의 세부 사항을 살펴보기 전에 가정이나 사무실에서 태양 광 또는 백업 전원 공급 장치에 사용되는 '파워 인버터'와 혼동해서는 안됩니다.

로직 'NOT'게이트는 무엇입니까?

출력이 입력을 보완하는 단일 입력 및 단일 출력 논리 게이트입니다.

위의 정의에 따르면 입력이 'HIGH'또는 '1'또는 'true'또는 'positive signal'인 경우 출력은 'LOW'또는 '0'또는 'false'또는 'negative signal'이됩니다.

입력이 'LOW'또는 '0'또는 'false'또는 'negative signal'인 경우 출력은 'HIGH'또는 '1'또는 'true'또는 'positive signal'으로 반전됩니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리가 아닌 게이트의 그림 :

'A'가 입력이고 'Y'가 출력이라고 가정 해 봅시다. 논리 NOT 게이트의 부울 방정식은 다음과 같습니다. Ā = Y.

방정식은 출력이 입력의 반전임을 나타냅니다.

논리가 아닌 게이트에 대한 진리표 :

| 에 (입력) | 와이 (산출) |

| 0 | 1 |

| 1 | 0 |

not gate는 항상 단일 입력을 가지며 (항상 단일 출력을 가짐) 의사 결정 장치로 분류됩니다. 삼각형 끝에있는 'o'기호는 보완 또는 반전을 나타냅니다.

이 'o'기호는 논리 'NOT'게이트로 제한 될뿐만 아니라 모든 논리 게이트 또는 모든 디지털 회로에서 사용할 수 있습니다. 'o'가 입력에 있으면 입력이 액티브 로우임을 나타냅니다.

Active-Low : 'LOW'입력이 주어지면 출력이 활성화됩니다 (트랜지스터, LED 또는 릴레이 등 활성화).

NAND 및 NOR 게이트 동등 :

'NOT'게이트는 모든 입력 핀을 결합하여 논리 'NAND'및 논리 'NOR'게이트를 사용하여 구성 할 수 있습니다. 이는 입력 핀이 3, 4 이상인 게이트에 적용됩니다.

트랜지스터 기반 로직 'NOT'게이트 :

논리 'NOT'은 NPN 트랜지스터와 1K 저항으로 구성 할 수 있습니다. 트랜지스터베이스에 'HIGH'신호를 적용하면 접지가 트랜지스터의 콜렉터에 연결되어 출력이 'LOW'가됩니다.

트랜지스터의베이스에“LOW”신호를 적용하면 트랜지스터는 OFF 상태로 유지되고 접지에 연결되지 않지만 출력은 Vcc에 연결된 풀업 저항에 의해“HIGH”가됩니다. 따라서 트랜지스터를 사용하여 논리 'NOT'게이트를 만들 수 있습니다.

슈미트 인버터 :

슈미트 인버터의 활용 및 기능을 설명하기 위해 자동 배터리 충전기로이 개념을 탐색합니다. 리튬 이온 배터리 충전 절차의 예를 들어 보겠습니다.

3.7V 리튬 이온 배터리는 배터리가 3V ~ 3.2V에 도달하면 충전됩니다. 배터리 전압은 충전하는 동안 점차적으로 상승하고 배터리는 4.2V에서 차단되어야합니다. 충전 후 배터리의 개방 회로 전압은 약 4.0V로 떨어집니다. .

전압 센서는 차단 한계를 측정하고 릴레이를 트리거하여 충전을 중지합니다. 그러나 전압이 4.2V 아래로 떨어지면 충전기는 충전되지 않은 것으로 감지하고 4.2V까지 충전을 시작하고 차단합니다. 다시 배터리 전압이 4.0V로 떨어지고 충전이 다시 시작되고이 광기는 계속 반복됩니다.

이렇게하면 배터리가 빠르게 소모됩니다.이 문제를 극복하려면 배터리가 3V에서 3.2V로 떨어질 때까지 배터리가 충전을 시작하지 않도록 낮은 임계 값 레벨 또는 'LTV'가 필요합니다. 상위 임계 전압 또는 'UTV'는 다음과 같습니다. 이 예에서는 4.2V입니다.

Schmitt 인버터는 전압이 상위 임계 전압을 통과 할 때 출력 상태를 전환하도록 만들어지며 입력이 하위 임계 전압에 도달 할 때까지 동일하게 유지됩니다.

마찬가지로 입력이 하한 임계 전압을 통과하면 입력이 상한 임계 전압에 도달 할 때까지 출력이 동일하게 유지됩니다.

LTV와 UTV 사이의 상태는 변경되지 않습니다.

이제 이로 인해 ON / OFF가 훨씬 더 부드러워지고 원하지 않는 진동이 제거되고 회로가 전기적 노이즈에 더 강해집니다.

Schmitt NOT 게이트 발진기 :

위의 회로는 33 % 듀티 사이클에서 구형파를 생성하는 발진기입니다. 처음에는 커패시터가 방전 된 상태이고 접지 신호는 NOT 게이트의 입력에서 사용할 수 있습니다.

출력은 양으로 바뀌고 저항 'R'을 통해 커패시터를 충전하고, 커패시터는 인버터의 상한 임계 전압까지 충전되어 상태를 변경하고, 출력은 음의 신호가되고 커패시터 전압이 도달 할 때까지 저항 'R'을 통해 방전되기 시작합니다 임계 레벨이 낮아지고 상태가 변경되면 출력이 양수로 바뀌고 커패시터를 충전합니다.

이 사이클은 회로에 전원이 공급되는 동안 반복됩니다.

위 오실레이터의 주파수는 다음과 같이 계산할 수 있습니다. F = 680 / RC

여기서 F는 주파수입니다.

R은 옴 단위의 저항입니다.

C는 패러 드 단위의 커패시턴스입니다.

구형파 변환기 :

위의 회로는 사인파 신호를 구형파로 변환하며 실제로 모든 아날로그 파를 구형파로 변환 할 수 있습니다.

두 저항 R1 및 R2는 전압 분배기로 작동하며 바이어스 포인트를 얻는 데 사용되며 커패시터는 모든 DC 신호를 차단합니다.

입력 신호가 상한 임계 값 레벨을 초과하거나 하한 임계 값 레벨 미만이되면 출력이 켜집니다.

신호에 따라 LOW 또는 HIGH, 이것은 구형파를 생성합니다.

IC 7404 NOT 게이트 인버터 :

IC 7404는 게이트 IC가 아닌 가장 일반적으로 사용되는 로직 중 하나입니다. 핀은 14 개, 핀 # 7은 접지, 핀 # 14는 Vcc입니다. 작동 전압은 4.5V ~ 5V입니다.

전파 지연 :

전파 지연은 게이트가 입력을 제공 한 후 출력을 처리하는 데 걸리는 시간입니다.

논리에서 'NOT'게이트는 상태를 HIGH에서 LOW로 또는 그 반대로 변경하는 데 약 22 나노초가 걸립니다.

몇 가지 다른 논리 'NOT 게이트 IC :

• 74LS04 Hex Inverting NOT Gate

• 74LS14 Hex Schmitt 반전 게이트 아님

• 74LS1004 Hex 반전 드라이버

• CD4009 Hex Inverting NOT Gate

• CD4069 Hex Inverting NOT Gate

OR 게이트 작동 방식

이제 디지털 로직 OR 게이트에 대해 살펴 보겠습니다. 기본 정의, 기호, 진리표, 다중 입력 OR 게이트를 살펴보고 2 입력 OR 게이트를 기반으로 트랜지스터를 구성하고 마지막으로 OR 게이트 IC 7432에 대해 살펴 보겠습니다.

“전류계를 만드는 방법 ”

로직 'OR'게이트는 무엇입니까?

OR 게이트의 모든 입력이 'LOW'또는 '0'또는 'false'또는 '일 때 출력이'LOW '또는'0 '또는'false '로 바뀌거나'negative signal '을 제공하는 전자 게이트입니다. 부정적인 신호”.

예 : 입력 수가 'n'인 OR 게이트를 말하면 모든 입력이 'LOW'이면 출력이 'LOW'가됩니다. 한 입력이 'HIGH'또는 '1'또는 'true'또는 'positive signal'인 경우에도 출력은 'HIGH'또는 '1'또는 'true'로 바뀌거나 'positive signal'을 제공합니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리 OR 게이트 기호 그림 :

여기서 'A'와 'B'는 두 개의 입력이고 'Y'는 출력입니다.

논리 OR 게이트에 대한 부울 표현식 : 출력 'Y'는 두 개의 입력 'A'와 'B'를 더한 것입니다. (A + B) = Y.

부울 더하기는 (+)로 표시됩니다.

‘A’가‘1’이고‘B’가‘1’이면 출력은 (A + B) = 1 + 1 =‘1’또는 '높음'입니다.

‘A’가‘0’이고‘B’가‘1’이면 출력은 (A + B) = 0 + 1 =‘1’또는 '높음'입니다.

‘A’가‘1’이고‘B’가‘0’이면 출력은 (A + B) = 1 + 0 =‘1’또는 '높음'입니다.

‘A’가‘0’이고‘B’가‘0’이면 출력은 (A + B) = 0 + 0 =‘0’또는 '낮음'입니다.

위의 조건은 진리표에서 단순화되었습니다.

진리표 (두 입력) :

| A (입력) | B (입력) | Y (출력) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

3- 입력 'OR'게이트 :

3 개의 입력 OR 게이트 그림 :

논리 OR 게이트는 'n'개의 입력을 가질 수 있습니다. 즉, 2 개 이상의 입력을 가질 수 있습니다 (로직 OR 게이트에는 최소 2 개의 입력과 항상 1 개의 출력이 있음).

3 개의 입력 논리 OR 게이트의 경우 부울 방정식은 다음과 같이 바뀝니다. (A + B + C) = Y, 4 개 이상의 입력에 대해 유사합니다.

3 개의 입력 로직 OR 게이트에 대한 진리표 :

| A (입력) | B (입력) | C (입력) | Y (출력) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

다중 입력 논리 또는 게이트 :

시판되는 로직 OR 게이트는 2, 3 및 4 입력에서만 사용할 수 있습니다. 입력이 4 개 이상이면 게이트를 계단식으로 연결해야합니다.

다음과 같이 2 개의 입력 OR 게이트를 계단식으로 연결하여 6 개의 입력 로직 OR 게이트를 가질 수 있습니다.

이제 위 회로의 부울 방정식은 Y = (A + B) + (C + D) + (E + F)가됩니다.

그래도 언급 된 모든 논리적 규칙은 위의 회로에 적용됩니다.

위의 6 개 입력 OR 게이트에서 5 개의 입력 만 사용하려는 경우 한 핀에 풀다운 저항을 연결할 수 있으며 이제 5 개 입력 OR 게이트가됩니다.

트랜지스터 기반 2 개의 입력 논리 OR 게이트 :

이제 논리 OR 게이트가 어떻게 작동하는지 알았습니다. 두 개의 NPN 트랜지스터를 사용하여 2 개의 입력 OR 게이트를 구성 해 보겠습니다. 로직 IC는 거의 동일한 방식으로 구성됩니다.

2 개의 트랜지스터 OR 게이트 회로도 :

출력 'Y'에서 LED를 연결할 수 있습니다. 출력이 높으면 LED가 켜집니다 (LED + Ve 단자는 'Y'에 330ohm 저항이 있고 음은 GND에 있음).

두 트랜지스터의베이스에 LOW 신호를 적용하면 두 트랜지스터가 모두 꺼지고 접지 신호는 1k 풀다운 저항을 통해 T2 / T1의 이미 터에서 사용할 수 있으므로 출력이 LOW가됩니다.

트랜지스터 중 하나가 ON이면 T2 / T1의 이미 터에서 양의 전압을 사용할 수 있으므로 출력이 HIGH가됩니다.

이제 논리 OR 게이트를 직접 구성하는 방법을 알았습니다.

쿼드 OR 게이트 IC 7432 :

시장에서 로직 OR 게이트를 구매하려면 위의 구성을 사용하십시오.

핀 # 7과 핀 # 14는 각각 GND와 Vcc 인 14 개의 핀을 가지고 있습니다. 5V에서 작동합니다.

전파 지연 :

전파 지연은 출력이 LOW에서 HIGH로 또는 그 반대로 변경되는 데 걸리는 시간입니다.

LOW에서 HIGH 로의 전파 지연은 섭씨 25도에서 7.4 나노초입니다.

HIGH에서 LOW 로의 전파 지연은 섭씨 25도에서 7.7 나노초입니다.

• 74LS32 쿼드 2 입력

• CD4071 쿼드 2 입력

• CD4075 트리플 3 입력

• CD4072 듀얼 4 입력

논리 독점 –OR 게이트

이 게시물에서는 논리 XOR 게이트 또는 Exclusive-OR 게이트에 대해 살펴 보겠습니다. 기본 정의, 기호, 진리표, XOR 등가 회로, 논리 NAND 게이트를 사용한 XOR 구현을 살펴보고 마지막으로 쿼드 2 입력 Ex-OR 게이트 IC 7486에 대해 살펴 보겠습니다.

이전 게시물에서 우리는 세 가지 기본 논리 게이트 'AND', 'OR'및 'NOT'에 대해 배웠습니다. 또한이 세 가지 기본 게이트를 사용하여 두 개의 새로운 논리 게이트 'NAND'및 'NOR'을 구성 할 수 있음을 배웠습니다.

이 둘은 기본 게이트가 아니지만 두 개의 논리 게이트가 더 있지만 다른 논리 게이트의 조합으로 구성되며 Boolean 방정식은 매우 중요하고 매우 유용하여 별개의 논리 게이트로 간주됩니다.

이 두 논리 게이트는 '배타적 OR'게이트와 '배타적 NOR'입니다. 이 게시물에서는 논리 배타적 OR 게이트에 대해서만 살펴 보겠습니다.

'독점 OR'게이트는 무엇입니까?

두 논리 입력이 서로 다를 때 출력이 'high'또는 '1'또는 'true'로 바뀌거나 'positive signal'을 제공하는 전자 게이트입니다 (이는 2 개의 2 입력 Ex에만 적용됩니다. -OR 게이트).

예 : '2 개'입력이있는 배타적 OR 게이트를 말하면 입력 핀 A 중 하나가 'HIGH'이고 입력 핀 B가 'LOW'이면 출력이 'HIGH'또는 '1'또는 'true'로 바뀝니다. '긍정적 인 신호'.

두 입력이 동일한 로직 레벨 인 경우, 즉 두 핀 모두 'HIGH'또는 두 핀 모두 'LOW'이면 출력이 'LOW'또는 '0'또는 'false'또는 'negative signal'으로 바뀝니다.

노트 :

'High', '1', 'positive signal', 'true'라는 용어는 본질적으로 동일합니다 (Positive 신호는 배터리 또는 전원 공급 장치의 양극 신호 임).

'낮음', '0', '부정 신호', '거짓'이라는 용어는 기본적으로 동일합니다 (부정 신호는 배터리 또는 전원 공급 장치의 부 신호 임).

논리 배타적 OR 게이트 그림 :

여기서 'A'와 'B'는 두 개의 입력이고 'Y'는 출력입니다.

논리 Ex-OR 게이트에 대한 부울 식 : Y = (A.) ̅B + A.B̅

‘A’가‘1’이고‘B’가‘1’이면 출력은 (A̅.B + A.B̅) = 0 x 1 + 1 x 0 =‘1’또는 'LOW'입니다.

‘A’가‘0’이고‘B’가‘1’이면 출력은 (A̅.B + A.B̅) = 1 x 1 + 0 x 0 =‘1’또는“HIGH”입니다.

‘A’가‘1’이고‘B’가‘0’이면 출력은 (A̅.B + A.B̅) = 0 x 0 + 1 x 1 =‘1’또는“HIGH”입니다.

‘A’가‘0’이고‘B’가‘0’이면 출력은 (A̅.B + A.B̅) = 1 x 0 + 0 x 1 =‘0’또는 '낮음'입니다.

위의 조건은 진리표에서 단순화되었습니다.

진리표 (두 입력) :

| A (입력) | B (입력) | Y (출력) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

위의 두 입력 로직 Ex-OR 게이트에서 두 입력이 서로 다르면 즉 '1'과 '0'출력이 'HIGH'가됩니다. 그러나 3 개 이상의 입력 로직 Ex-OR 또는 일반적으로 Ex-OR의 출력은 ODD 수의 로직 'HIGH'가 게이트에 적용될 때만 'HIGH'가됩니다.

예 : 3 개의 입력 Ex-OR 게이트가있는 경우 하나의 입력에만 논리 'HIGH'를 적용하면 (논리 '1'의 홀수) 출력이 'HIGH'가됩니다. 논리 'HIGH'를 두 개의 입력에 적용하면 (이것은 논리 '1'의 짝수) 출력이 'LOW'가되는 식으로 계속됩니다.

3 입력 전용 OR 게이트 :

3 개의 입력 EX-OR 게이트 그림 :

3 개의 입력 로직 EX-OR 게이트에 대한 진리표 :

| A (입력) | B (입력) | C (입력) | Y (출력) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

3 입력 Ex-OR 게이트의 경우 부울 방정식은 다음과 같습니다. A (BC) ̅ + A̅BC̅ + (AB) ̅C + ABC

앞에서 설명한 것처럼 로직 'Ex-OR'게이트는 기본 로직 게이트가 아니라 서로 다른 로직 게이트의 조합입니다. Ex-OR 게이트는 다음과 같이 논리 'OR'게이트, 논리 'AND'게이트 및 논리 'NAND'게이트를 사용하여 구현할 수 있습니다.

'독점 OR'게이트의 등가 회로 :

위의 설계에는 큰 단점이 있습니다. 하나의 Ex-OR 게이트를 만들려면 3 개의 다른 논리 게이트가 필요합니다. 그러나 로직 NAND 게이트만으로 Ex-OR 게이트를 구현하여이 문제를 극복 할 수 있으며, 이는 또한 제작하기에 경제적입니다.

NAND 게이트를 사용하는 독점 OR 게이트 :

독점 OR 게이트는 산술 연산, 전체 가산기, 반가산기 등 복잡한 컴퓨팅 작업을 수행하는 데 사용되며 수행 기능도 제공 할 수 있습니다.

논리 전용 또는 게이트 IC 7486 :

시장에서 로직 Ex-OR 게이트를 구매하려는 경우 위의 DIP 구성이 제공됩니다.

핀 # 7과 핀 # 14는 각각 GND와 Vcc 인 14 개의 핀을 가지고 있습니다. 5V에서 작동합니다.

전파 지연 :

전파 지연은 입력을 제공 한 후 출력이 LOW에서 HIGH로 또는 그 반대로 변경되는 데 걸리는 시간입니다.

LOW에서 HIGH 로의 전파 지연은 23 나노초입니다.

HIGH에서 LOW 로의 전파 지연은 17 나노초입니다.

일반적으로 사용 가능한 'EX-OR'게이트 IC :

- 74LS86 쿼드 2 입력

- CD4030 쿼드 2 입력

여전히 질문이있는 경우 위의 자세한 설명이 논리 게이트가 무엇인지, 논리 게이트가 어떻게 작동하는지 이해하는 데 도움이 되었기를 바랍니다. 댓글란에 적어 주시면 빠른 답변을 받으실 수 있습니다.

Previous : 커패시터 누설 테스터 회로 – 누설 커패시터를 빠르게 찾기 다음 : 디지털 버퍼 – 작동, 정의, 진리표, 이중 반전, 팬 아웃