약식 연산 증폭기는 연산 증폭기입니다 그리고 그것은 또한 차동 증폭기 . Op-Amp는 다양한 전자 회로의 필수 구성 요소입니다. 연산 증폭기는 수학적 연산 및 필터링, 신호 컨디셔닝을 수행하는 데 사용되는 선형 장치입니다. 이 장치는 외부에서 사용하도록 설계되었습니다. 전기 및 전자 부품 저항기, 커패시터 및 i / p 및 o / p 단자와 같은 것입니다. 이러한 구성 요소는 증폭기의 작동 및 기능 결과와 저항성 또는 정전 용량과 같은 변경된 피드백 구성의 이점을 조절하며, 증폭기는 다른 작업을 수행 할 수 있으며이를 연산 증폭기라고합니다. 안 연산 증폭기는 + &-로 표시되는 반전 및 비 반전 두 터미널의. 이 증폭기의 주요 기능은 두 입력 전압 간의 변화를 강화한다는 것입니다. 그러나 두 입력에 상호 작용하는 모든 전압을 무효화합니다.

차동 증폭기

차동 증폭기

모든 연산 증폭기는 i / p 구성으로 인해 차동 증폭기입니다. 첫 번째 전압 신호가 i / p 단자에 연결되고 나머지 신호가 반대쪽 i / p 단자에 연결되면 결과 o / p 전압은 다음과 같습니다. 두 i / p 전압 신호의 차이와 관련하여 출력 전압은 각 입력을 0V 접지에 연결하여 계산할 수 있습니다. 중첩 정리 .

차동 증폭기 회로

트랜지스터를 이용한 차동 증폭기 회로

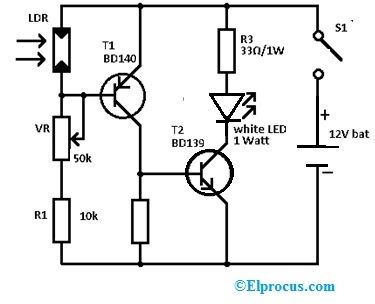

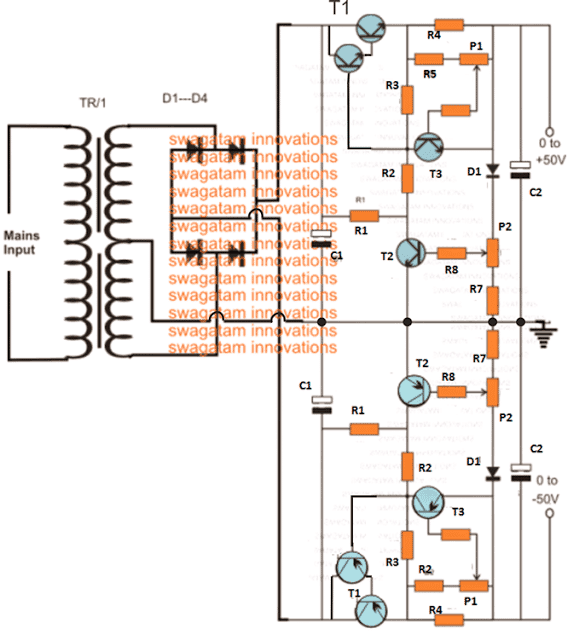

차동 증폭기 회로 BJT 사용에 대해 자세히 설명하고 더 나은 이해를 위해 적절한 방정식과 함께 회로도를 제공합니다. 다음 회로는 트랜지스터로 설계 두 i / p 신호 간의 차이를 제공합니다.

BJT를 사용한 차동 증폭기 회로

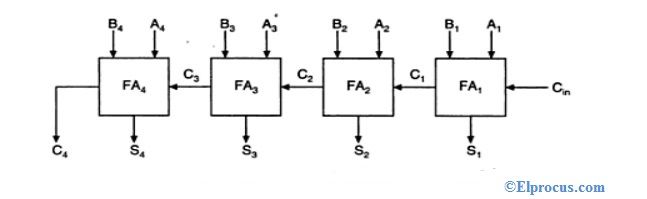

위의 회로도에서 보듯이 회로는 2 개의 입력과 2 개의 출력, 즉 I / P1, I / P2 및 O / P1, O / P2로 구성됩니다. 입력 I / P1은 T1 트랜지스터의베이스 단자에 적용되고 IP2는 T2 트랜지스터의베이스 단자에 적용됩니다. 두 트랜지스터의 이미 터 단자는 상호 이미 터 저항에 연결되어 두 개의 i / p 신호에 의해 두 개의 o / p 단자가 손상됩니다. 회로의 두 공급 전압은 Vcc 및 Vss입니다. 회로는 단일 전압 공급 장치에서도 작동하며 회로에 접지 단자가 없음을 확인할 수 있습니다.

차동 증폭기의 작동

트랜지스터가있는 차동 증폭기의 작동은 다음과 같습니다.

첫 번째 입력 신호가 T1 트랜지스터에 적용되면 콜렉터 저항 (RCOL1)에 걸쳐 높은 전압 강하가 발생하고 트랜지스터 T1의 콜렉터는 양이 적습니다. input1이 음수이면 트랜지스터 T1이 꺼지고 컬렉터 저항 RCOL1의 전압 강하가 매우 낮아지고 트랜지스터 T1의 컬렉터가 더 양수가됩니다.

BJT를 사용한 차동 증폭기 회로의 작동

따라서 삽입 된 o / p가 input1에 신호를 적용하기 위해 트랜지스터 T1의 콜렉터에 나타날 것이라고 결론을 내릴 수 있습니다. 트랜지스터 T1이 input1의 양의 값에 의해 켜지면 저항 REM을 통과하는 전류는 에미 터 전류가 콜렉터 전류와 동일하게 증가합니다.

따라서 저항 REM 양단의 전압 강하는 증가하고 T1, T2 트랜지스터의 에미 터가 양의 방향으로 흐릅니다. 트랜지스터 T2를 만드는 것은 트랜지스터의베이스를 네거티브로 만드는 것과 동일합니다. 그 조건에서 T2 트랜지스터는 더 적은 전류로 동작하여 RCOL2에서 전압 강하가 적어 지므로 트랜지스터 T2의 콜렉터는 + Ve 방향으로 이동합니다. + Ve i / p 신호. 따라서 비 반전 단자의 o / p가 T1의베이스에서 입력을 위해 T2 트랜지스터의 컬렉터에 나타난다는 결론을 내릴 수 있습니다. 트랜지스터의 증폭은 위의 회로에 표시된 두 트랜지스터 T1 및 T2의 컬렉터를 o / p b / n 취함으로써 다르게 구동 될 수 있습니다.

두 트랜지스터가 모든 특성에서 동일하다고 가정하고 전압이 동일한 경우 (VBASE1 = VBASE2) 트랜지스터의 이미 터 전류도 동일하다고 할 수 있습니다.

IEM1 = IEM2

총 이미 터 전류 (IE) = IEM1 + IEM2

VEM = VBASE-VBASE 입력

IEM = (VBASE-VBASE IN) / REM

트랜지스터의 이미 터 전류는 트랜지스터의 hfe 값에 관계없이 거의 일정하게 유지됩니다. ICOL1 IEM1 및 ICOL2 IEM2, ICOL1 ICOL2부터.

또한 VCOL1 = VCOL2 = VCC – ICOL RCOL (컬렉터 저항 RCOL1 = RCOL2 = RCOL로 가정).

차동 증폭기 회로는 두 신호 간의 분산을 증가시키는 폐쇄 루프 증폭기입니다. 이러한 회로는 계측 시스템에 매우 적합합니다. 차동 증폭기는 높은 CMRR (공통 모드 제거 비율)과 높은 i / p 임피던스를 가지고 있습니다. 차동 증폭기는 하나 또는 두 개의 연산 증폭기를 사용하여 설계 할 수 있습니다.

따라서 이것은 차동 증폭기 회로 BJT 트랜지스터를 사용합니다. 우리는 당신이이 개념을 더 잘 이해했다고 믿습니다. 또한이 주제에 대한 의문 사항이 있으시면 아래 댓글 섹션에 의견을 남겨 귀중한 제안을 해주십시오. 여기에 질문이 있습니다. 차동 증폭기의 응용 분야는 무엇입니까?