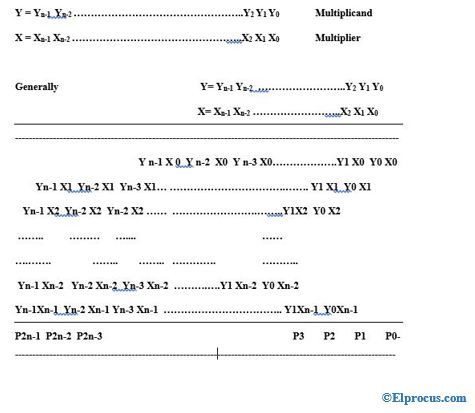

캐스 코드 증폭기 아날로그 회로의 성능을 향상시키는 데 사용됩니다. cascode의 활용은 진공관뿐만 아니라 트랜지스터의 응용에 사용될 수있는 일반적인 방법입니다. 제비 갈매기는 1939 년 Roger Wayne Hickman과 Frederick Vinton Hunt가 쓸 수있는 기사에서 사용되었습니다. 전압 안정기 응용 프로그램. 그들은 2 개의 3 극관에 대한 캐스 코드를 투영했는데, 1 차는 공통 음극의 설정이고 다음은 5 극 대신 공통 그리드입니다. 따라서 이것의 이름은 pentode와 같은 관련 특성을 갖는 계단식 3 극관의 감소로 가정 할 수 있습니다.

Cascode 증폭기는 무엇입니까?

캐스 코드 증폭기는 다음과 같은 2 단계를 포함합니다. CE (공통 이미 터) 무대와 CB (공통베이스) CE가 CB에 공급하는 단계. 단일 단계와 비교했을 때 증폭기 ,이 조합은 높은 입력 / 출력 절연, 높은 i / p 임피던스, 높은 o / p 임피던스 및 높은 대역폭과 같은 다른 특성을 가질 수 있습니다.

전류 회로에서이 증폭기는 두 개의 트랜지스터를 사용하여 자주 사용할 수 있습니다. BJT 그렇지 않으면 FET. 여기서 하나의 트랜지스터는 CE 또는 공통 소스처럼 작동하는 반면 다른 트랜지스터는 CB 또는 공통 게이트처럼 작동합니다. 이 증폭기는 O / P에서 I / P 로의 직선 결합이없는 것처럼 I / O 격리를 향상시켜 밀러 효과를 줄여 높은 대역폭을 제공합니다.

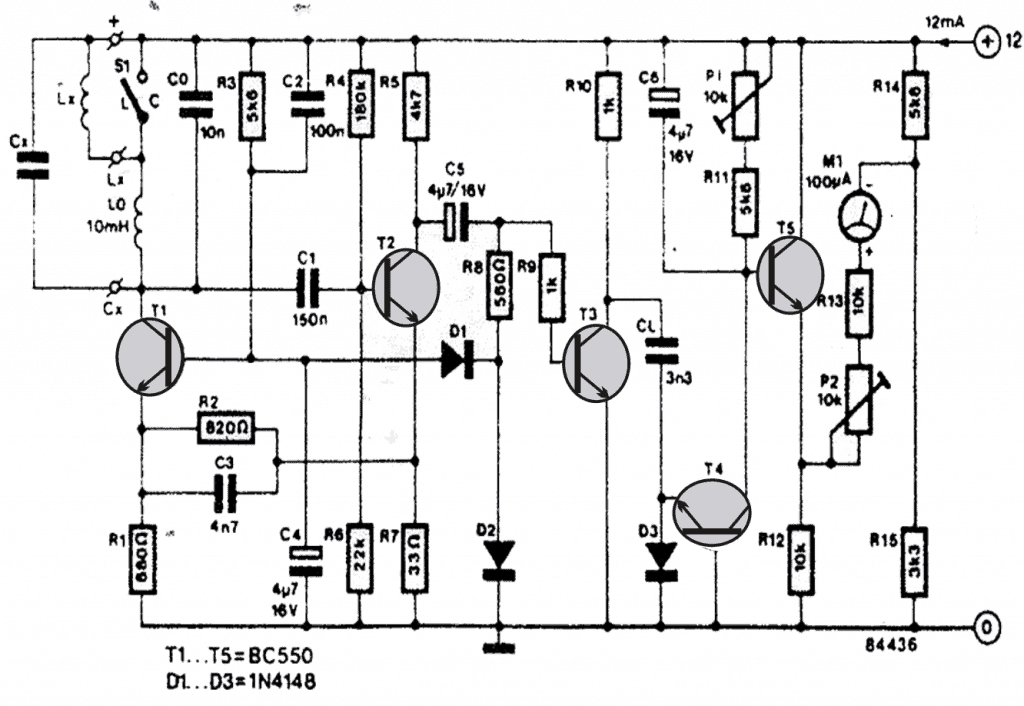

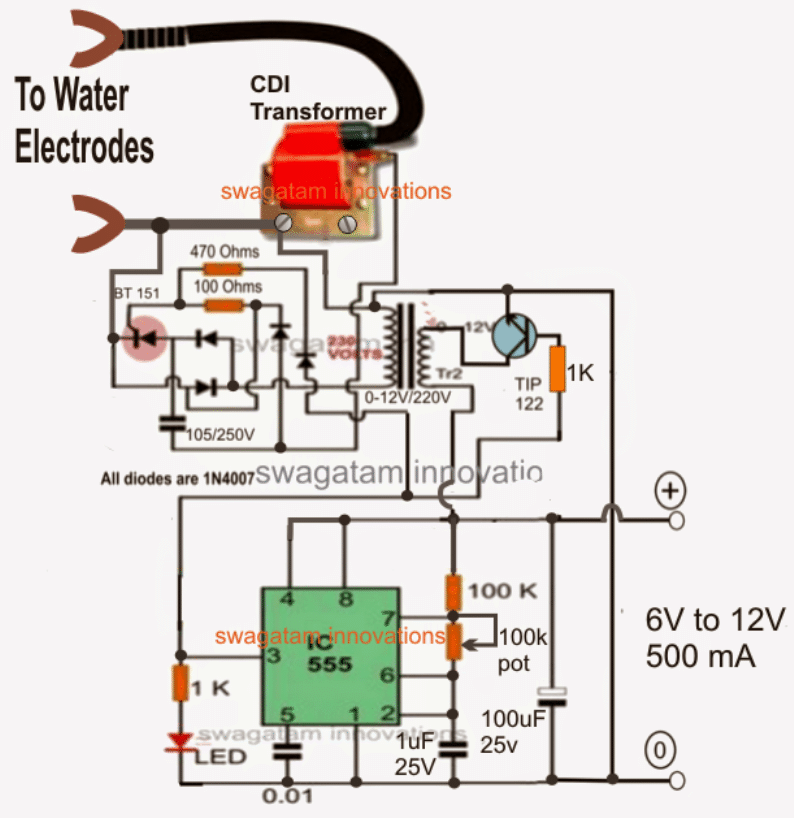

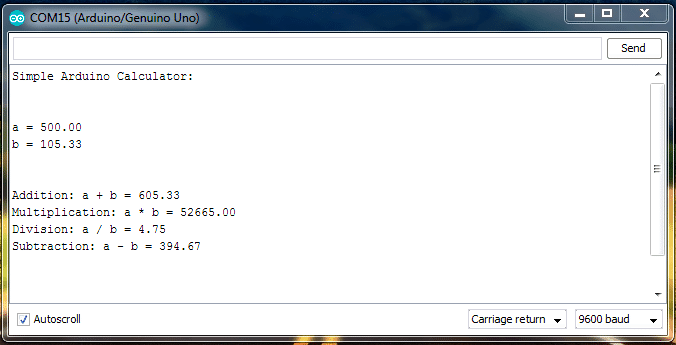

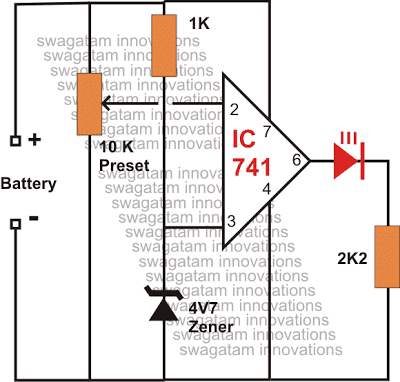

Cascode 증폭기 회로

FET를 사용하는 Cascode 증폭기 회로는 다음과 같습니다. 이 증폭기의 입력 단계는 FET & Vin (입력 전압)은 게이트 단자에 연결됩니다. 이 증폭기의 출력단은 입력 위상에 의해 야심 찬 FET의 공통 게이트입니다. o / p 스테이지의 드레인 저항은 Rd이고 Vout (출력 전압)은 2 차 트랜지스터의 드레인 단자에서 가져올 수 있습니다.

Q2 트랜지스터의 게이트 단자가 접지되면 트랜지스터의 소스 전압과 드레인 전압이 거의 안정적으로 유지됩니다. 즉, 더 높은 Q2 트랜지스터는 더 낮은 Q1 트랜지스터에 대해 낮은 i / p 저항을 제공합니다. 이것은 낮은 트랜지스터의 이득을 감소시키고 따라서 밀러 효과도 감소합니다. 그래서 대역폭이 증가합니다.

캐스 코드 증폭기 회로

낮은 게인 감소 트랜지스터 상부 트랜지스터가 보상하기 때문에 총 이득에 영향을 미치지 않습니다. 드레인에서 소스 드리프트 커패시턴스로의 충전 및 방전이 드레인을 사용하여 수행 될 수 있으므로 상부 트랜지스터는 밀러 효과의 영향을받지 않습니다. 저항기 . 주파수 응답과 부하는 단순히 고주파에 영향을 미쳤습니다.

이 회로에서는 입력에서 출력을 분리 할 수 있습니다. 하부 트랜지스터는 소스 및 드레인 단자에서 거의 안정적인 전압을 포함하는 반면 상부 트랜지스터는 두 단자에서 거의 안정적인 전압을 포함합니다. 기본적으로 O / P에서 IP 로의 피드백은 없습니다. 따라서 두 단자는 안정적인 전압의 중간 연결을 사용하여 잘 절연됩니다.

장점과 단점

장점은 다음과 같습니다.

이 증폭기는 높은 대역폭, 이득, 슬 루율, 안정성 및 입력 임피던스를 제공합니다. 2- 트랜지스터 회로의 경우 부품 수가 매우 적습니다.

단점은 다음과 같습니다.

이 증폭기는 2 개가 필요합니다 트랜지스터 고전압 공급으로. 2- 트랜지스터 캐스 코드의 경우, 두 개의 트랜지스터가 처리중인 충분한 VDS를 통해 바이어스되어야하므로 전압 공급에 대한 제한이 낮아집니다.

따라서 이것은 캐스 코드 증폭기 이론. 이 증폭기는 접힌 cascode-amplifier 및 bimos cascode-amplifier와 같은 두 가지 유형으로 제공됩니다. 캐스 코드 증폭기 주파수 응답에 대한 질문이 있습니까?