운영 증폭기 다양한 구성으로 제공됩니다. ㅏ 가산 증폭기 최소 2개 이상의 입력에서 사용 가능한 전압을 단일 o/p 전압으로 결합하는 데 사용되는 유형 중 하나입니다. 반전 연산 증폭기에는 반전 입력 단자에 제공되는 단일 입력 전압이 있습니다. 반전 입력 단자에 여러 개의 입력 저항을 제공하면 각 입력은 합산 증폭기로 알려진 원래 입력 저항 값과 동일합니다. 이 증폭기는 전압의 가산 및 감산을 처리합니다. 합산 증폭기에는 두 가지 유형이 있습니다. 반전과 비반전. 이 문서에서는 다음 사항에 대한 간략한 정보를 제공합니다. 비반전 합산 증폭기 , 작업 및 해당 응용 프로그램.

비반전 합산 증폭기란 무엇입니까?

동일한 위상 또는 극성을 갖는 합산 출력을 제공하는 데 사용되는 연산 증폭기 회로 구성 유형을 비반전 합산 증폭기라고 합니다. 이러한 유형의 합산 증폭기는 소스 신호가 Op-Amp에 연결되어 전달됨을 나타내는 직접 결합 기술을 활용합니다.

이러한 유형의 연산 증폭기 구성에서는 연산 증폭기의 반전 입력이 접지됩니다. 비반전 입력은 저항을 통해 또는 직접 입력 전압과 연결됩니다. 이 비반전 합산 증폭기의 출력 전압은 다음 공식을 사용하여 결정할 수 있습니다.

Vout = (1+Rf/R1)*Vin

여기서 'Rf'는 피드백 저항이고 'R1'은 입력 저항이고 Vin은 적용된 입력 전압의 합입니다.

비반전 합산 증폭기 작동

비반전 합산 증폭기는 유사한 극성(또는) 위상을 포함하는 i/p 신호의 합산된 o/p를 제공합니다. 이 증폭기에는 여러 입력 소스와 이러한 입력이 저항을 통해 비반전 단자에 연결되는 단일 출력이 있습니다.

모든 입력 신호는 저항에 직접 연결되는 반면 모든 저항의 다른 쪽 끝은 단순히 연산 증폭기의 비반전 단자에 연결됩니다. 그 후 합산 접합은 피드백 저항을 통해 GND에 연결됩니다. 따라서 이 배열을 사용하면 연산 증폭기가 저항 값에 따라 결정되는 적절한 가중치를 사용하여 다양한 입력 전압을 추가할 수 있습니다.

이 증폭기의 총 출력은 연결된 모든 입력 전압의 합입니다. 여기서 개별 가중치는 등가 입력이 있는 연결된 저항기에 따라 달라집니다. 따라서 이 증폭기의 입력과 출력은 0°의 위상을 갖습니다.

연산 증폭기를 사용한 비반전 합산 증폭기

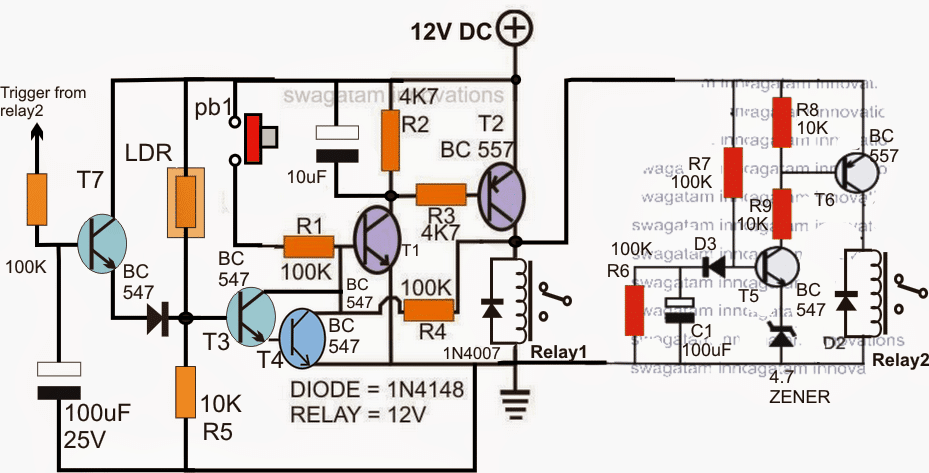

비반전 합산 증폭기 회로도는 아래와 같습니다. 이 증폭기 구성은 비반전 증폭기와 유사합니다. 이 증폭기의 입력 전압은 연산 증폭기의 비반전 입력 단자에 제공됩니다. 이 증폭기의 출력은 전압 분배기 바이어스 피드백을 통해 반전 입력 단자로 피드백됩니다. 이 회로에는 편의상 3개의 입력이 있지만 입력 개수를 추가할 수도 있습니다. 이 증폭기의 출력 전압 계산은 아래에 설명되어 있습니다.

“전기 집진기 작동 원리 ”

'VIN'과 같은 입력 전압이 모든 입력 신호의 조합이라면 이는 연산 증폭기의 비반전 핀에 제공될 수 있습니다. 위의 비반전 합산 증폭기 회로에서 입력 핀 VIN을 사용하여 이 증폭기의 출력 전압을 계산할 수 있으며 피드백 분배기에는 Rf 및 Ri 저항이 사용됩니다. 따라서 출력 전압은 다음과 같습니다.

VOUT = VIN (1 + (Rf / Ri))

이 증폭기의 출력 전압을 알아낼 때마다 VIN 값을 결정해야 합니다. 세 가지 주요 입력 소스가 V1, V2 및 V3이고 입력 저항이 다음과 같은 경우; R1, R2 및 R3의 경우 다른 동등한 채널이 접지되면 각 채널 입력은 VIN1, VIN2 및 VIN3입니다. 따라서,

VIN = VIN1 + VIN2 + VIN3

여기서 가상 접지 아이디어가 적용되지 않으면 모든 채널이 나머지 채널에 영향을 미칩니다. 먼저 VIN의 VIN1 부분을 쉬운 수학으로 계산해야 합니다. VIN2와 VIN3의 나머지 두 값을 쉽게 얻을 수 있습니다.

V2 및 V3가 VIN1에 접지될 때마다 등가 저항은 전압 분배기 네트워크를 형성할 때 무시할 수 없습니다. 따라서,

VIN1 = V1 [(R2 || R3) / (R1 + (R2 || R3))]

마찬가지로 다른 두 VIN2 및 VIN3 값을 다음과 같이 계산할 수 있습니다.

VIN2 = V2 [(R1 || R3) / (R2 + (R1 || R3))]

VIN3 = V3 [(R1 || R2) / (R3 + (R1 || R2))]

그러므로,

VIN = VIN1 + VIN2 + VIN3

VIN = V1 [(R2 || R3) / (R1 + (R2 || R3))] + V2 [(R1 || R3) / (R2 + (R1 || R3))] + V3 [(R1 || R2) / (R3 + (R1 || R2))].

마지막으로 출력 전압을 다음과 같이 계산할 수 있습니다.

VOUT = VIN (1 + (Rf / Ri))

VOUT = (1 + (Rf / Ri)) {V1 [(R2 || R3) / (R1 + (R2 || R3))] + V2 [(R1 || R3) / (R2 + (R1 || R3 ))] + V3 [(R1 || R2) / (R3 + (R1 || R2))]}

모든 저항이 비슷한 값을 갖는 특별한 등가 가중치 상태를 고려하면 VOUT은 다음과 같습니다.

VOUT = (1 + (Rf / Ri)) ((V1 + V2 + V3)/3)

비반전 합산 회로 설계는 주로 필요한 전압 이득을 갖도록 이 증폭기를 설계하는 방식으로 접근됩니다. 그 후, 사용되는 연산 증폭기의 종류에 맞게 입력 저항을 가능한 한 크게 선택합니다.

비반전 합산 증폭기 전달 함수

3개의 입력을 갖는 비반전 합산 증폭기 회로는 다음과 같습니다. 세 개의 입력 신호를 증폭기에 추가하려는 경우 세 개의 입력 비반전 합산 증폭기의 전달 함수는 아래에서 설명됩니다.

중첩 정리를 사용하여 먼저 이 회로 내에 단순히 'V1'을 남겨두고 R2 및 R3 저항을 GND에 연결하여 V2 및 V3를 0으로 만듭니다.

완벽한 연산 증폭기의 경우 비반전 단자의 입력 전류는 0으로 간주됩니다. 따라서 R1, R2 및 R3 저항은 R2 및 R3 저항을 통해 병렬로 전압 감쇠기를 만듭니다. 그래서 'Vp'는;

Vp = V1 R2 || R3/ R1+ R2|| R3

R2는 어디에 || R3 우리는 R2와 R3 값이 평행하다는 것을 알아냈습니다.

V1 입력 소스를 사용하면 연산 증폭기의 출력은 VOUT1을 통해 기록될 수 있으며 다음과 같이 쓸 수 있습니다.

VOUT1 = Vp [1+ Rf2/Rf1]

VOUT1 방정식에 Vp 값을 대입하면 다음을 얻을 수 있습니다.

VOUT1 = V1 (R2 || R3/ R1+ R2|| R3) [1+ Rf2/Rf1]

마찬가지로 입력 신호만 있을 때 VOUT2 & VOUT3을 쓸 수 있습니다. 이에 따라 V2 및 V3.

VOUT2 = V2 (R1 || R3/ R2+ R1|| R3) [1+ Rf2/Rf1]

VOUT3 = V3 (R1 || R2/ R3+ R1|| R2) [1+ Rf2/Rf1]

위의 VOUT1, VOUT2 및 VOUT3 방정식을 추가하면 3개의 입력 신호를 포함하는 비반전 증폭기의 전달 함수는 다음과 같습니다.

VOUT = [1+ Rf2/Rf1] V1 (R2 || R3/ R1+ R2|| R3) + V2 (R1 || R3/ R2+ R1|| R3) + V3 (R1 || R2/ R3+ R1|| R2) .

반전 및 비반전 합산 증폭기의 차이점

반전 및 비반전 합산 증폭기의 주요 차이점은 아래에 설명되어 있습니다.

| 반전 합산 증폭기 | 비반전 합산 증폭기 |

| 이 회로의 모든 입력 신호는 연산 증폭기의 반전 입력 단자에 제공되고 비반전 단자는 접지됩니다. | 이 회로의 모든 입력 신호는 연산 증폭기의 비반전 입력 단자에 제공되고 반전 단자는 접지됩니다. |

| 이 합산 증폭기는 반전 연산 증폭기와 유사하게 작동합니다. | 이 비반전 합산 증폭기는 비반전 연산 증폭기와 유사하게 작동합니다. |

| 합산 증폭기를 반전시키면 출력 신호의 위상이 반전됩니다. | 비반전 합산 증폭기는 입력 신호와 유사한 위상을 유지합니다. |

| 이 증폭기 구성은 적용된 입력 전압의 음의 합을 제공합니다. | 비반전 합산 증폭기 구성은 적용된 입력 전압의 양의 합을 제공합니다. |

| 이 증폭기의 위상차는 입력 신호와 출력 신호 사이의 180°입니다. | 이 증폭기의 입력 신호와 출력 신호 사이의 위상차는 0°입니다. |

| 이 증폭기의 피드백은 입력 신호가 제공되는 곳에 제공됩니다. | 이 증폭기의 피드백과 입력 신호는 서로 다른 단자에 연결됩니다. |

| '+' 단자는 GND에 연결됩니다. | 이 앰프에서는 '-' 단자가 GND에 연결되어 있습니다. |

| 이 증폭기에서는 피드백을 GND에 연결할 수 없습니다. | 이 증폭기의 피드백은 저항기를 통해 GND에 연결됩니다. |

| 이 증폭기는 음극(-ve) 극성의 반전된 출력을 제공합니다. | 이 증폭기에서 생성된 출력은 반전되지 않고 +ve 극성으로 표현됩니다. |

| 이 증폭기의 이득 극성은 (-)입니다. | 비반전 증폭기의 이득 극성은 (+) 양입니다. |

| 이 증폭기의 이득은 < 또는 > 또는 =(1)입니다. | 이득은 항상 > 1입니다. |

장점

그만큼 비반전 합산 증폭기의 장점 다음을 포함합니다.

- 이 합산 증폭기 전압 이득은 양수입니다.

- 위상 반전 없이 출력 신호를 얻을 수 있습니다.

- 입력 임피던스 값이 높습니다.

- 전압이득은 가변적이다.

- 이 증폭기에서는 우수한 임피던스 정합을 얻을 수 있습니다.

그만큼 비반전 합산 증폭기의 단점 다음을 포함합니다.

- 이 증폭기에는 입력 중 하나가 분리되면 연결된 나머지 채널에 대해 회로 이득이 두 배가 된다는 주요 단점이 있습니다.

- 모든 입력을 분리하는 동안 비반전 핀의 플로팅을 벗어나는 것은 권장되지 않습니다.

- 심각도의 변화에 따라 입력과 다른 입력 사이에 간섭이 발생할 수 있습니다.

- 세 번째 입력을 도입하면 처음 두 채널 내에서 게인이 감소할 수 있으며 이는 특정 애플리케이션에 따라 영향을 미칠 수 있습니다.

- 가변 출력 임피던스 값을 갖는 소스에 대한 링크가 있는 경우 나머지 두 채널의 증폭에 영향을 미치므로 널리 사용되지 않을 수 있습니다.

응용

그만큼 비반전 합산 증폭기의 응용 다음을 포함합니다.

- 비반전 합산 연산 증폭기 회로는 높은 입력 임피던스가 필요한 모든 곳에 적용 가능합니다.

- 이러한 회로는 인버터처럼 반전 입력에 o/p를 제공하기만 하면 전압 팔로워로 사용할 수 있습니다.

- 이러한 회로는 특정 계단식 회로를 분리하는 데 도움이 됩니다.

- 이 증폭기는 동일한 위상 또는 극성을 갖는 적용된 입력 신호에 대한 합산 출력을 제공하는 데 사용됩니다.

따라서 이것은 비반전 합산의 개요입니다. 증폭기, 회로, 파생 , 차이점, 전달 기능, 장점, 단점 및 응용 분야. 이는 +ve 비반전 입력에 대한 여러 입력이 있는 일종의 합산 증폭기입니다. 합산 증폭기는 저항을 통한 다양한 입력 신호를 연산 증폭기의 비반전 입력에 연결하기만 하면 비반전 합산 증폭기로 활용할 수 있습니다.

이 합산 증폭기의 출력 전압은 저항기 값에 의해 바이어스된 입력 전압의 양입니다. 이 증폭기의 모든 입력 신호는 간단히 저항에 연결될 수 있는 반면, 각 저항의 나머지 단자는 연산 증폭기의 비반전 단자에 연결될 수 있습니다. 그 후 합산 접합은 피드백 저항을 통해 GND에 연결됩니다. 따라서 이러한 배열을 통해 연산 증폭기는 저항 값을 통해 결정된 적절한 가중치를 통해 다양한 입력 전압을 포함할 수 있습니다. 여기에 질문이 있습니다. 합산 증폭기란 무엇입니까?